**WS63V100 系列 Wi-Fi、BLE 和 SLE Combo 芯片**

# **硬件用户指南**

文档版本 04

发布日期 2024-09-29

# 前言

## 概述

本文档主要介绍 WS63V100 系列芯片的封装管脚信息、电气特性参数、原理图设计建议、PCB 设计建议、热设计建议、焊接工艺、潮敏参数、接口时序、注意事项等内容。

本文主要为技术服务工程师提供硬件设计的参考。

## 产品版本

与本文档相对应的产品版本如下。

| 产品名称  | 产品版本 | 描述                        |

|-------|------|---------------------------|

| WS63  | V100 | 常规版本芯片，支持 WiFi、BLE、SLE 等。 |

| WS63E | V100 | 雷达版本芯片，基于常规版本芯片，增加雷达检测功能。 |

## 读者对象

本文档主要适用于以下工程师：

- 单板硬件开发工程师

- 软件工程师

- 技术支持工程师

## 符号约定

在本文中可能出现下列标志，它们所代表的含义如下。

| 符号 | 说明                                                                    |

|----|-----------------------------------------------------------------------|

|    | 表示如不避免则将会导致死亡或严重伤害的具有高等级风险的危害。                                        |

|    | 表示如不避免则可能导致死亡或严重伤害的具有中等级风险的危害。                                        |

|    | 表示如不避免则可能导致轻微或中度伤害的具有低等级风险的危害。                                        |

|    | 用于传递设备或环境安全警示信息。如不避免则可能会导致设备损坏、数据丢失、设备性能降低或其它不可预知的结果。<br>“须知”不涉及人身伤害。 |

|    | 对正文中重点信息的补充说明。<br>“说明”不是安全警示信息，不涉及人身、设备及环境伤害信息。                       |

## 修改记录

| 文档版本 | 发布日期       | 修改说明                                                                                                                                                                                                                  |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04   | 2024-09-29 | <ul style="list-style-type: none"><li>更新“1.2.8 UART 管脚”小节内容。</li><li>更新“1.2.10 GPIO 复用管脚”小节内容。</li><li>更新“2.2 极限工作条件”小节内容。</li><li>更新“2.5 上下电要求”小节内容。</li><li>更新“8.4 SPI 时序”小节内容。</li><li>更新“9.1 硬件设计”小节内容。</li></ul> |

| 03   | 2024-07-01 | <ul style="list-style-type: none"><li>更新“2.5 上下电要求”小节内容。</li><li>更新“4.5 RF 布线指导”小节内容。</li></ul>                                                                                                                       |

| 02   | 2024-06-03 | <ul style="list-style-type: none"><li>更新“2.4 DC/AC 电气参数”小节内容。</li></ul>                                                                                                                                               |

| 文档版本  | 发布日期       | 修改说明                                                                                                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |            | <ul style="list-style-type: none"><li>更新“3.1 小系统设计建议”小节内容。</li><li>更新“3.2 电源参考设计”小节内容。</li><li>更新“3.3.1 UART 接口”小节内容。</li><li>更新“4.6 时钟布线指导”小节内容。</li><li>更新“8.1 UART 时序”小节内容。</li></ul>                       |

| 01    | 2024-04-15 | <p>第一次正式版本版本发布。</p> <ul style="list-style-type: none"><li>更新“2.5 上下电要求”小节内容。</li><li>更新“3.1.1 时钟参考设计”小节内容。</li><li>更新“4.3 PCB 布局”小节内容。</li><li>更新“5.1 工作条件”小节内容。</li></ul>                                     |

| 00B07 | 2024-03-29 | <ul style="list-style-type: none"><li>更新“1.2.8 UART 管脚”小节内容。</li><li>更新“1.2.10 GPIO 复用管脚”小节内容。</li><li>更新“3.6 RFI 设计”小节内容。</li><li>更新“4.5 RF 布线指导”小节内容。</li></ul>                                              |

| 00B06 | 2024-02-22 | <ul style="list-style-type: none"><li>更新“1.2.6 RF 接口”小节内容。</li><li>更新“2.2 极限工作条件”小节内容。</li><li>更新“2.5 上下电要求”小节内容。</li><li>更新“3.2.1 电源方案”小节内容。</li><li>更新“5.2 电路热设计参考”小节内容。</li><li>更新“9.1 硬件设计”小节内容。</li></ul> |

| 00B05 | 2024-01-10 | <ul style="list-style-type: none"><li>更新“3.1.1 时钟参考设计”小节内容。</li><li>更新“3.6 RFI 设计”小节内容。</li></ul>                                                                                                              |

| 00B04 | 2023-12-27 | 更新“3.1.1 时钟参考设计”小节内容。                                                                                                                                                                                          |

| 00B03 | 2023-12-18 | 更新“1.2.5 电源管脚”小节内容。                                                                                                                                                                                            |

| 00B02 | 2023-11-21 | <ul style="list-style-type: none"><li>更新“2.4 DC/AC 电气参数”小节内容。</li><li>更新“4.6 时钟布线指导”小节内容。</li></ul>                                                                                                            |

| 00B01 | 2023-09-11 | 第一次临时版本发布。                                                                                                                                                                                                     |

# 目 录

|                        |    |

|------------------------|----|

| <b>前言 .....</b>        | i  |

| <b>1 封装与管脚 .....</b>   | 1  |

| 1.1 封装与管脚分布 .....      | 1  |

| 1.1.1 封装 .....         | 1  |

| 1.1.2 管脚分布 .....       | 5  |

| 1.2 管脚描述 .....         | 6  |

| 1.2.1 管脚类型说明 .....     | 6  |

| 1.2.2 管脚排列表 .....      | 8  |

| 1.2.3 PMU 控制信号 .....   | 9  |

| 1.2.4 GPIO 管脚 .....    | 9  |

| 1.2.5 电源管脚 .....       | 10 |

| 1.2.6 RF 接口 .....      | 11 |

| 1.2.7 GND 管脚 .....     | 11 |

| 1.2.8 UART 管脚 .....    | 12 |

| 1.2.9 ADC 通道 .....     | 12 |

| 1.2.10 GPIO 复用管脚 ..... | 13 |

| 1.2.11 CLK 管脚 .....    | 16 |

| <b>2 电性能参数 .....</b>   | 18 |

| 2.1 电流分布 .....         | 18 |

| 2.2 极限工作条件 .....       | 18 |

| 2.3 推荐工作条件 .....       | 19 |

| 2.4 DC/AC 电气参数 .....   | 20 |

| 2.5 上下电要求 .....        | 22 |

|                         |           |

|-------------------------|-----------|

| <b>3 原理图设计建议.....</b>   | <b>26</b> |

| 3.1 小系统设计建议.....        | 26        |

| 3.1.1 时钟参考设计 .....      | 26        |

| 3.1.2 复位电路 .....        | 30        |

| 3.1.3 硬件初始化系统配置电路 ..... | 31        |

| 3.2 电源参考设计 .....        | 33        |

| 3.2.1 电源方案 .....        | 33        |

| 3.2.2 电源规格 .....        | 36        |

| 3.2.3 AVDD33 电源.....    | 38        |

| 3.2.4 VBAT_IN 电源.....   | 40        |

| 3.2.5 DVDD3318 电源 ..... | 40        |

| 3.2.6 内部电源滤波电路 .....    | 41        |

| 3.2.7 BUCK 电源 .....     | 42        |

| 3.2.8 RF 电源.....        | 43        |

| 3.2.9 注意事项 .....        | 44        |

| 3.3 外围接口设计建议.....       | 44        |

| 3.3.1 UART 接口.....      | 44        |

| 3.3.2 PWM 接口.....       | 45        |

| 3.3.3 I2S 接口 .....      | 46        |

| 3.3.4 QSPI&SPI 接口.....  | 46        |

| 3.3.5 I2C 接口.....       | 47        |

| 3.3.6 ADC 接口.....       | 47        |

| 3.4 控制信号应用参考设计 .....    | 48        |

| 3.5 RFIO 设计 .....       | 48        |

| 3.6 RFI 设计 .....        | 49        |

| <b>4 PCB 设计建议.....</b>  | <b>51</b> |

| 4.1 叠层和布局.....          | 51        |

| 4.2 Fanout 封装设计建议 ..... | 53        |

| 4.3 PCB 布局 .....        | 55        |

| 4.4 电源 .....            | 57        |

| 4.5 RF 布线指导 .....       | 58        |

|                       |           |

|-----------------------|-----------|

| 4.6 时钟布线指导 .....      | 60        |

| 4.7 GND 布线指导 .....    | 60        |

| 4.8 屏蔽罩 .....         | 61        |

| <b>5 热设计建议 .....</b>  | <b>62</b> |

| 5.1 工作条件 .....        | 62        |

| 5.2 电路热设计参考 .....     | 63        |

| 5.2.1 器件布局 .....      | 63        |

| 5.2.2 PCB .....       | 64        |

| <b>6 焊接工艺 .....</b>   | <b>65</b> |

| 6.1 概述 .....          | 65        |

| 6.2 无铅回流焊工艺参数要求 ..... | 66        |

| 6.3 混合回流焊工艺参数要求 ..... | 68        |

| <b>7 潮敏参数 .....</b>   | <b>70</b> |

| 7.1 存放与使用 .....       | 70        |

| 7.2 重新烘烤 .....        | 71        |

| <b>8 接口时序 .....</b>   | <b>73</b> |

| 8.1 UART 时序 .....     | 73        |

| 8.2 I2C 时序 .....      | 74        |

| 8.3 I2S 时序 .....      | 76        |

| 8.4 SPI 时序 .....      | 76        |

| <b>9 注意事项 .....</b>   | <b>78</b> |

| 9.1 硬件设计 .....        | 78        |

| 9.2 单板生产工艺 .....      | 79        |

| <b>A 缩略语 .....</b>    | <b>80</b> |

# 1

## 封装与管脚

### 1.1 封装与管脚分布

#### 1.2 管脚描述

## 1.1 封装与管脚分布

### 1.1.1 封装

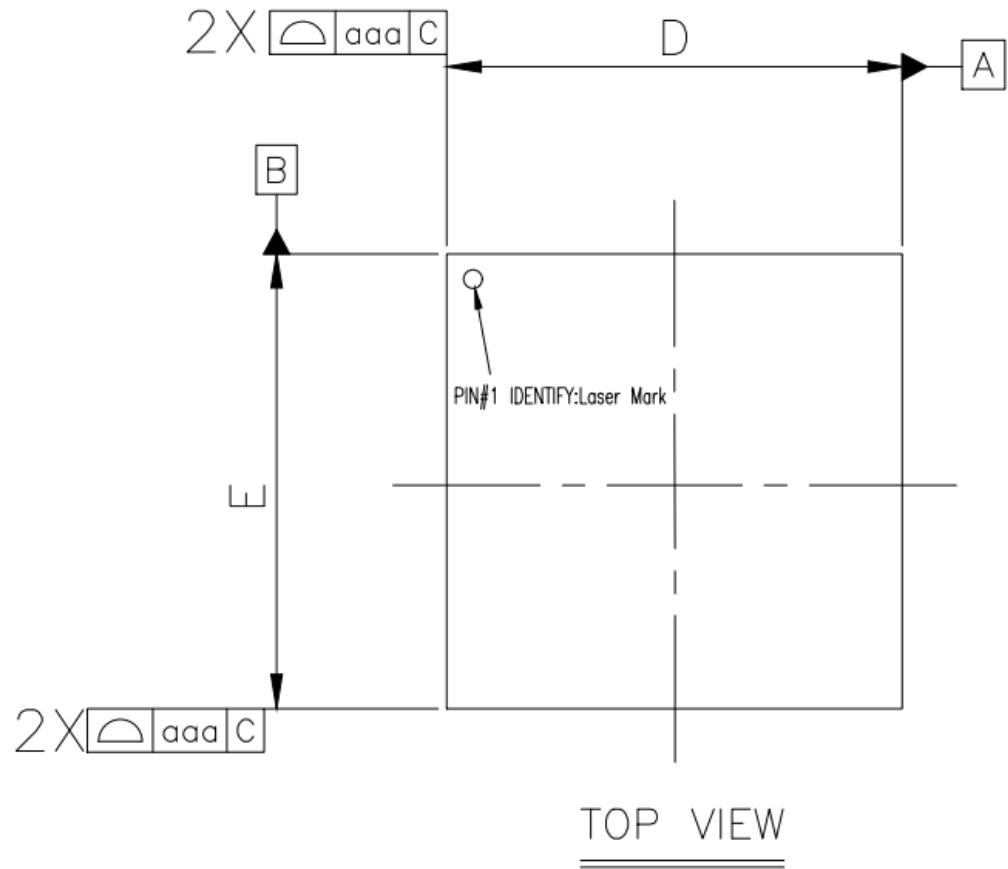

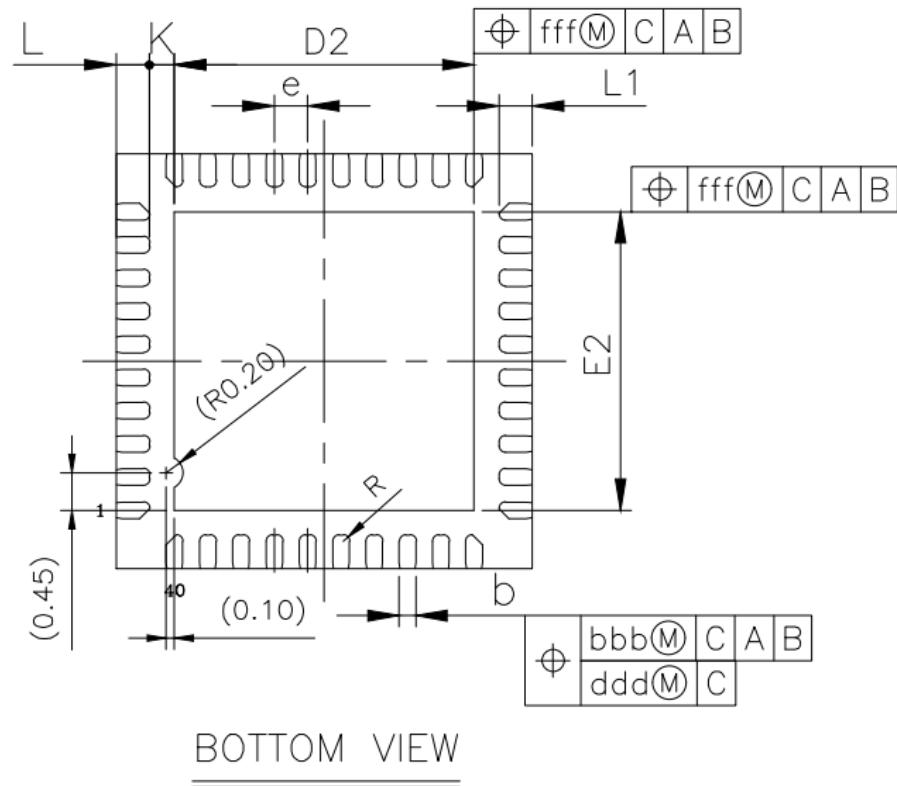

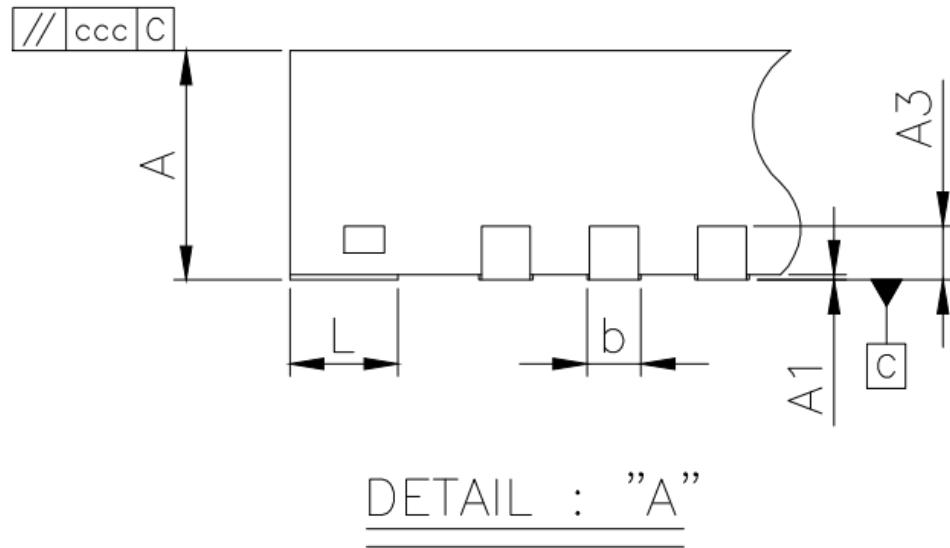

WS63V100 系列芯片采用 QFN40 封装，封装尺寸为 5mm×5mm，管脚间距为 0.4mm，

详细封装请参见图 1-1、图 1-2 和图 1-3。

图1-1 芯片封装顶视图

图1-2 芯片封装底视图

图1-3 芯片侧面放大图

芯片封装尺寸参数如表 1-1 所示。

表1-1 芯片封装参数说明表

| 参数 | 最小值<br>(mm) | 典型值<br>(mm) | 最大值<br>(mm) | 最小值<br>(inch) | 典型值<br>(inch) | 最大值<br>(inch) |  |

|----|-------------|-------------|-------------|---------------|---------------|---------------|--|

| A  | 0.85        | 0.90        | 0.95        | 0.033         | 0.035         | 0.037         |  |

| A1 | 0.00        | 0.02        | 0.05        | 0.000         | 0.001         | 0.002         |  |

| A3 | 0.20 REF    |             |             | 0.008 REF     |               |               |  |

| b  | 0.15        | 0.20        | 0.25        | 0.006         | 0.008         | 0.010         |  |

| D  | 4.90        | 5.00        | 5.10        | 0.193         | 0.197         | 0.201         |  |

| E  | 4.90        | 5.00        | 5.10        | 0.193         | 0.197         | 0.201         |  |

| D2 | 3.50        | 3.60        | 3.70        | 0.138         | 0.142         | 0.146         |  |

| E2 | 3.50        | 3.60        | 3.70        | 0.138         | 0.142         | 0.146         |  |

| e  | 0.40 BSC    |             |             | 0.016 BSC     |               |               |  |

| L  | 0.30        | 0.40        | 0.50        | 0.012         | 0.016         | 0.020         |  |

| L1 | 0.30        | 0.40        | 0.50        | 0.012         | 0.016         | 0.020         |  |

| K  | 0.20        |             |             | 0.008         |               |               |  |

| R  | 0.08        | -           | 0.13        | 0.003         | -             | 0.005         |  |

| 参数  | 最小值<br>(mm) | 典型值<br>(mm) | 最大值<br>(mm) | 最小值<br>(inch) | 典型值<br>(inch) | 最大值<br>(inch) |

|-----|-------------|-------------|-------------|---------------|---------------|---------------|

| aaa | 0.10        |             |             | 0.004         |               |               |

| bbb | 0.07        |             |             | 0.003         |               |               |

| ccc | 0.10        |             |             | 0.004         |               |               |

| ddd | 0.05        |             |             | 0.002         |               |               |

| eee | 0.08        |             |             | 0.003         |               |               |

| fff | 0.10        |             |             | 0.004         |               |               |

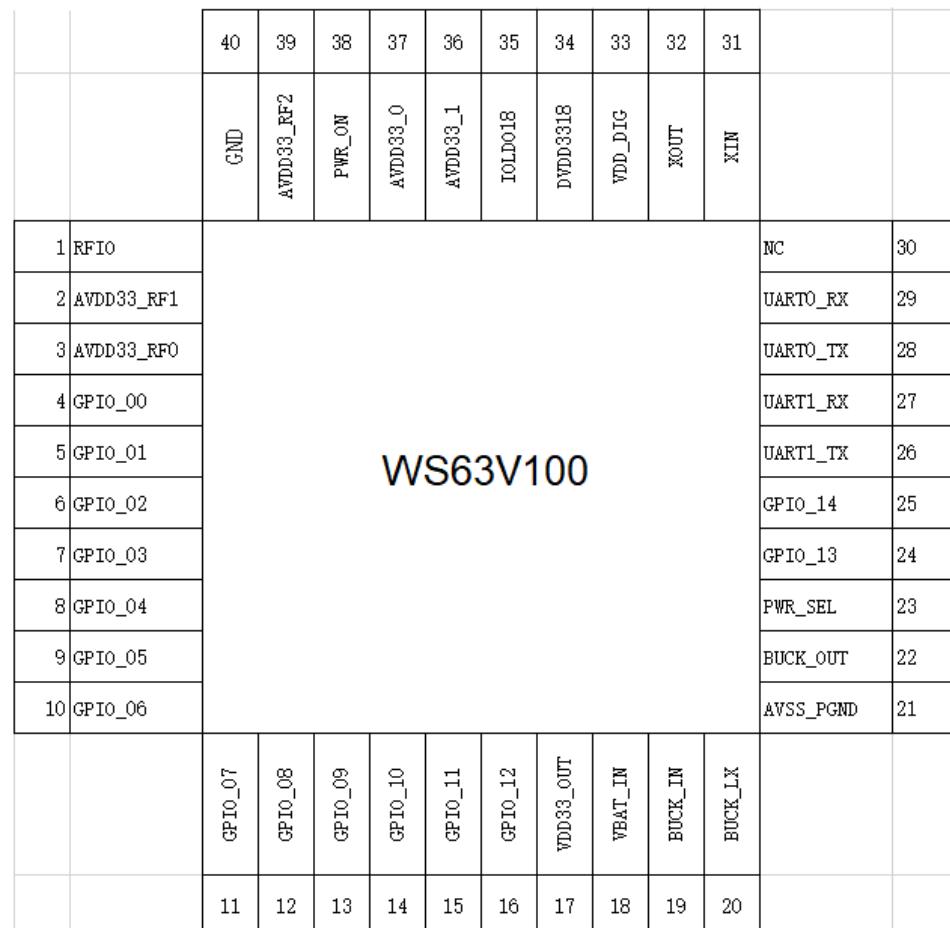

### 1.1.2 管脚分布

WS63V100 系列芯片管脚分布如图 1-4 和图 1-5 所示。

图1-4 WS63V100 TOP View 管脚分布

图1-5 WS63EV100 TOP View 管脚分布

|    |            |            |         |          |          |         |           |         |         |         |           |    |

|----|------------|------------|---------|----------|----------|---------|-----------|---------|---------|---------|-----------|----|

|    | 40         | 39         | 38      | 37       | 36       | 35      | 34        | 33      | 32      | 31      |           |    |

|    | RFI        | AVDD33_RF2 | PWR_ON  | AVDD33_0 | AVDD33_1 | TOLDO18 | DVDD3318  | VDD_DIG | XOUT    | XIN     |           |    |

| 1  | RFIO       |            |         |          |          |         |           |         |         |         | NC        | 30 |

| 2  | AVDD33_RF1 |            |         |          |          |         |           |         |         |         | UART0_RX  | 29 |

| 3  | AVDD33_RFO |            |         |          |          |         |           |         |         |         | UART0_TX  | 28 |

| 4  | GPIO_00    |            |         |          |          |         |           |         |         |         | UART1_RX  | 27 |

| 5  | GPIO_01    |            |         |          |          |         |           |         |         |         | UART1_TX  | 26 |

| 6  | GPIO_02    |            |         |          |          |         |           |         |         |         | GPIO_14   | 25 |

| 7  | GPIO_03    |            |         |          |          |         |           |         |         |         | GPIO_13   | 24 |

| 8  | GPIO_04    |            |         |          |          |         |           |         |         |         | PWR_SEL   | 23 |

| 9  | GPIO_05    |            |         |          |          |         |           |         |         |         | BUCK_OUT  | 22 |

| 10 | GPIO_06    |            |         |          |          |         |           |         |         |         | AVSS_PGND | 21 |

|    | GPIO_07    | GPIO_08    | GPIO_09 | GPIO_10  | GPIO_11  | GPIO_12 | VDD33_OUT | VBAT_IN | BUCK_IN | BUCK_LX |           |    |

|    | 11         | 12         | 13      | 14       | 15       | 16      | 17        | 18      | 19      | 20      |           |    |

## 说明

WS63V100 常规版本芯片 PIN40 管脚为 GND, WS63EV100 雷达版本芯片 PIN40 管脚为 RFI。

## 1.2 管脚描述

### 1.2.1 管脚类型说明

管脚 I/O 类型说明如表 1-2 所示。

表1-2 管脚 I/O 类型说明

| I/O | 说明    |

|-----|-------|

| I   | 输入信号。 |

| I/O                              | 说明                       |

|----------------------------------|--------------------------|

| I <sub>PD</sub>                  | 输入信号，内部下拉。               |

| I <sub>PU</sub>                  | 输入信号，内部上拉。               |

| I <sub>S</sub>                   | 输入信号，带施密特触发器。            |

| I <sub>SPD</sub>                 | 输入信号，带施密特触发器，内部下拉。       |

| I <sub>SPU</sub>                 | 输入信号，带施密特触发器，内部上拉。       |

| O                                | 输出信号。                    |

| O <sub>OD</sub>                  | 输出，漏极开路。                 |

| I/O                              | 双向输入/输出信号。               |

| I <sub>PD</sub> /O               | 双向，输入下拉。                 |

| I <sub>PU</sub> /O               | 双向，输入上拉。                 |

| I <sub>SPD</sub> /O              | 双向，输入下拉，带施密特触发器。         |

| I <sub>SPU</sub> /O              | 双向，输入上拉，带施密特触发器。         |

| I <sub>PD</sub> /O <sub>OD</sub> | 双向，输入下拉，输出漏极开路。          |

| I <sub>PU</sub> /O <sub>OD</sub> | 双向，输入上拉，输出漏极开路。          |

| I <sub>S</sub> /O                | 双向，输入带施密特触发器。            |

| I <sub>S</sub> /O <sub>OD</sub>  | 双向，输入带施密特触发器，输出漏极开路。     |

| CIN                              | Crystal Oscillator：晶振输入。 |

| COUT                             | Crystal Oscillator：晶振输出。 |

| P                                | 电源。                      |

| PI                               | 电源输入。                    |

| PO                               | 电源输出。                    |

| GND                              | 地。                       |

## 1.2.2 管脚排列表

WS63V100 系列芯片采用的封装形式为 QFN 40PIN，管脚按位置排列如表 1-3 所示。

表1-3 WS63EV100 芯片管脚排列

| 位置 | 管脚名称       | 位置   | 管脚名称       |

|----|------------|------|------------|

| 1  | RFIO       | 22   | BUCK_OUT   |

| 2  | AVDD33_RF1 | 23   | PWR_SEL    |

| 3  | AVDD33_RF0 | 24   | GPIO_13    |

| 4  | GPIO_00    | 25   | GPIO_14    |

| 5  | GPIO_01    | 26   | UART1_TX   |

| 6  | GPIO_02    | 27   | UART1_RX   |

| 7  | GPIO_03    | 28   | UART0_TX   |

| 8  | GPIO_04    | 29   | UART0_RX   |

| 9  | GPIO_05    | 30   | NC (保持悬空)  |

| 10 | GPIO_06    | 31   | XIN        |

| 11 | GPIO_07    | 32   | XOUT       |

| 12 | GPIO_08    | 33   | VDD_DIG    |

| 13 | GPIO_09    | 34   | DVDD3318   |

| 14 | GPIO_10    | 35   | IOLDO18    |

| 15 | GPIO_11    | 36   | AVDD33_1   |

| 16 | GPIO_12    | 37   | AVDD33_0   |

| 17 | VDD33_OUT  | 38   | PWR_ON     |

| 18 | VBAT_IN    | 39   | AVDD33_RF2 |

| 19 | BUCK_IN    | 40   | RFI        |

| 20 | BUCK_LX    | EPAD | GND        |

| 21 | AVSS_PGND  | -    | -          |

### 说明

- WS63V100 常规版本芯片 PIN40 管脚为 GND，板级可选择接地或 NC 悬空。

### 1.2.3 PMU 控制信号

全局控制信号如表 1-4 所示。

表1-4 全局控制信号管脚列表

| PIN | 名称      | 类型 | 电平 (V)  | 说明                                                                  |

|-----|---------|----|---------|---------------------------------------------------------------------|

| 38  | PWR_ON  | I  | 3.3/1.8 | PMU 上电使能管脚 (跟随 DVDD3318 电平)。<br>0: 下电;<br>1: 上电。                    |

| 23  | PWR_SEL | I  | 3.3     | VBAT_IN 电源方案选择管脚。<br>0: VBAT_IN 采用 5V 供电;<br>1: VBAT_IN 采用 3.3V 供电。 |

### 1.2.4 GPIO 管脚

GPIO 接口如表 1-5 所示。

表1-5 GPIO 管脚列表

| PIN | 名称      | 类型  | 电平(V)   | 说明                  |

|-----|---------|-----|---------|---------------------|

| 4   | GPIO_00 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 5   | GPIO_01 | I/O | 3.3/1.8 | 通用 GPIO, 管脚禁止加上拉电阻。 |

| 6   | GPIO_02 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 7   | GPIO_03 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 8   | GPIO_04 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 9   | GPIO_05 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 10  | GPIO_06 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 11  | GPIO_07 | I/O | 3.3/1.8 | 通用 GPIO。            |

| 12  | GPIO_08 | I/O | 3.3/1.8 | 通用 GPIO。            |

| PIN | 名称      | 类型  | 电平(V)   | 说明                 |

|-----|---------|-----|---------|--------------------|

| 13  | GPIO_09 | I/O | 3.3/1.8 | 通用 GPIO，管脚禁止加上拉电阻。 |

| 14  | GPIO_10 | I/O | 3.3/1.8 | 通用 GPIO。           |

| 15  | GPIO_11 | I/O | 3.3/1.8 | 通用 GPIO，管脚禁止加上拉电阻。 |

| 16  | GPIO_12 | I/O | 3.3/1.8 | 通用 GPIO。           |

| 24  | GPIO_13 | I/O | 3.3/1.8 | 通用 GPIO。           |

| 25  | GPIO_14 | I/O | 3.3/1.8 | 通用 GPIO。           |

## 1.2.5 电源管脚

电源管脚如表 1-6 所示。

表1-6 电源管脚列表

| PIN | 名称         | 类型    | 电压 (V)    | 说明                                                                                        |

|-----|------------|-------|-----------|-------------------------------------------------------------------------------------------|

| 2   | AVDD33_RF1 | PI    | 3.0 ~ 3.6 | RF 电源输入，外接滤波电容 1μF。                                                                       |

| 3   | AVDD33_RF0 | PI    | 3.0 ~ 3.6 | RF 电源输入，外接滤波电容 1μF。                                                                       |

| 17  | VDD33_OUT  | PI/PO | 3.0 ~ 3.6 | 芯片采用 VBAT_IN 5V 供电时，该管脚作为 3.3V 电源输出；芯片采用 VBAT_IN 3.3V 供电时，该管脚作为 3.3V 电源输入。管脚外接滤波电容 4.7μF。 |

| 18  | VBAT_IN    | PI    | 3.3/5     | 电源输入，可选择 5V 或 3.3V 供电，外接滤波电容 10μF。                                                        |

| 19  | BUCK_IN    | PI    | 3.0 ~ 3.6 | 电源输入，外接滤波电容 4.7μF。                                                                        |

| 20  | BUCK_LX    | -     | -         | LDO 方案下接电源 (3.3V)，BUCK 方案下接电感，外接 2.2uH 电感。                                                |

| 22  | BUCK_OUT   | PO    | 0.9       | 芯片内部 BUCK 输出，BUCK 电源方案下外接滤波电容 10μF，LDO                                                    |

| PIN | 名称         | 类型    | 电压 (V)    | 说明                                                                            |

|-----|------------|-------|-----------|-------------------------------------------------------------------------------|

|     |            |       |           | 电源方案下悬空。                                                                      |

| 33  | VDD_DIG    | PO    | 0.9       | 芯片内部电源输出，BUCK 电源方案下悬空，LDO 电源方案下外接滤波电容 1μF。                                    |

| 34  | DVDD3318   | PI    | 3.3/1.8   | IO 电源输入，外接滤波电容 4.7μF。                                                         |

| 35  | IOLDO18    | PI/PO | 1.8       | IO 电源输入为 3.3V 时，IOLDO 输出 1.8V；IO 电源输入为 1.8V 时，IOLDO 需输入 1.8V 电源。引脚外接滤波电容 1μF。 |

| 36  | AVDD33_1   | PI    | 3.0 ~ 3.6 | 电源输入，外接滤波电容 2.2μF。                                                            |

| 37  | AVDD33_0   | PI    | 3.0 ~ 3.6 | 电源输入，外接滤波电容 1μF。                                                              |

| 39  | AVDD33_RF2 | PI    | 3.0 ~ 3.6 | RF 电源输入，外接滤波电容 1μF。                                                           |

## 1.2.6 RF 接口

RF 接口如表 1-7 所示。

表1-7 RF 接口管脚列表

| PIN | 名称   | 类型  | 电平 (V) | 说明                  |

|-----|------|-----|--------|---------------------|

| 1   | RFIO | ANA | -      | WLAN 2.4G RF 输入/输出。 |

| 40  | RFI  | ANA | -      | WS63E 芯片雷达天线输入。     |

## 1.2.7 GND 管脚

GND 管脚如表 1-8 所示。

表1-8 GND 管脚列表

| PIN | 名称 | 电压 (V) | 说明 |

|-----|----|--------|----|

|     |    |        |    |

| PIN  | 名称        | 电压 (V) | 说明      |

|------|-----------|--------|---------|

| 21   | AVSS_PGND | -      | GND 管脚。 |

| EPAD | GND       | -      | GND 管脚。 |

## 1.2.8 UART 管脚

芯片独立的 UART0/1 管脚为耐 5V 管脚，输出管脚类型为 OD 开漏输出，使用时建议加 2.2KΩ 上拉电阻。可复用为 I2C 接口。

表1-9 GPIO 复用管脚

| PIN | 管脚名称     | 类型 | 电压 (V)    | 说明                                                      |

|-----|----------|----|-----------|---------------------------------------------------------|

| 26  | UART1_TX | OD | 5/3.3/1.8 | 复用信号 0: GPIO_15<br>复用信号 1: UART1_TX<br>复用信号 2: I2C1_SDA |

| 27  | UART1_RX | I  | 5/3.3/1.8 | 复用信号 0: GPIO_16<br>复用信号 1: UART1_RX<br>复用信号 2: I2C1_SCL |

| 28  | UART0_TX | OD | 5/3.3/1.8 | 复用信号 1: UART0_TX<br>复用信号 2: I2C0_SDA                    |

| 29  | UART0_RX | I  | 5/3.3/1.8 | 复用信号 1: UART0_RX<br>复用信号 2: I2C0_SCL                    |

## 1.2.9 ADC 通道

### 须知

ADC 管脚：LSADC 通道与 GPIO 功能只支持其中 1 种功能，ADC 通道管脚与 GPIO 管脚的对应关系如表 1-10 所示。

表1-10 ADC 通道管脚与复用管脚对应关系

| 复用管脚名称  | ADC 管脚 |

|---------|--------|

| GPIO_07 | ADC0   |

| GPIO_08 | ADC1   |

| GPIO_09 | ADC2   |

| GPIO_10 | ADC3   |

| GPIO_11 | ADC4   |

| GPIO_12 | ADC5   |

### 1.2.10 GPIO 复用管脚

GPIO (General Purpose Input/Output) 管脚如表 1-11 所示。其中 PIN5、7、8、10 为硬件配置字，使用时必需注意上电前的默认电平，详细设计请参见“3.1.3 硬件初始化系统配置电路”。

表1-11 GPIO 复用管脚

| PIN | 管脚名称    | 类型  | 电压 (V)  | 说明                                                                                              |

|-----|---------|-----|---------|-------------------------------------------------------------------------------------------------|

| 4   | GPIO_00 | I/O | 3.3/1.8 | 复用信号 0: GPIO_0 (Default)<br>复用信号 1: PWM0<br>复用信号 2: 保留<br>复用信号 3: SPI1_CS_N<br>复用信号 4: JTAG_TDI |

| 5   | GPIO_01 | I/O | 3.3/1.8 | 复用信号 0: GPIO_1 (Default)<br>复用信号 1: PWM1<br>复用信号 2: 保留<br>复用信号 3: SPI1_IO0/SPI1_OUT             |

| 6   | GPIO_02 | I/O | 3.3/1.8 | 复用信号 0: GPIO_2 (Default)<br>复用信号 1: PWM2<br>复用信号 2: 保留                                          |

| PIN | 管脚名称    | 类型  | 电压 (V)  | 说明                                                                                                                                                          |

|-----|---------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         |     |         | 复用信号 3: SPI1_IO3                                                                                                                                            |

| 7   | GPIO_03 | I/O | 3.3/1.8 | 复用信号 0: GPIO_3 (Default)<br>复用信号 1: PWM3<br>复用信号 2: 保留<br>复用信号 3: SPI1_IO1/SPI1_IN                                                                          |

| 8   | GPIO_04 | I/O | 3.3/1.8 | 复用信号 0: 保留 (Default)<br>复用信号 1: PWM4<br>复用信号 2: GPIO_4<br>复用信号 3: SPI1_IO1/SPI1_IN (优先使用 pin8)<br>复用信号 4: JTAG_ENABLE, 硬件配置字                                |

| 9   | GPIO_05 | I/O | 3.3/1.8 | 复用信号 0: 保留 (Default)<br>复用信号 1: PWM5<br>复用信号 2: UART2_CTS<br>复用信号 3: SPI1_IO2<br>复用信号 4: GPIO_5<br>复用信号 5: SPI0_IN                                          |

| 10  | GPIO_06 | I/O | 3.3/1.8 | 复用信号 0: GPIO_6 (Default)<br>复用信号 1: PWM6<br>复用信号 2: UART2_RTS<br>复用信号 3: SPI1_SCK<br>复用信号 4: REFCLK_FREQ_STATUS,<br>硬件配置字<br>复用信号 5: 保留<br>复用信号 6: SPI0_OUT |

| 11  | GPIO_07 | I/O | 3.3/1.8 | 复用信号 0: GPIO_7 (Default)<br>复用信号 1: PWM7                                                                                                                    |

| PIN | 管脚名称    | 类型  | 电压 (V)  | 说明                                                                                                                                                      |

|-----|---------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         |     |         | 复用信号 2: UART2_RXD<br>复用信号 3: SPI0_SCK<br>复用信号 4: I2S_MCLK                                                                                               |

| 12  | GPIO_08 | I/O | 3.3/1.8 | 复用信号 0: GPIO_8 (Default)<br>复用信号 1: PWM0<br>复用信号 2: UART2_TXD<br>复用信号 3: SPI0_CS1_N<br>复用信号 4: 保留                                                       |

| 13  | GPIO_09 | I/O | 3.3/1.8 | 复用信号 0: GPIO_9 (Default)<br>复用信号 1: PWM1<br>复用信号 2: RADAR_ANTO_SW<br>复用信号 3: SPI0_OUT<br>复用信号 4: I2S_DO<br>复用信号 5: 保留<br>复用信号 6: 保留<br>复用信号 7: JTAG_TDO |

| 14  | GPIO_10 | I/O | 3.3/1.8 | 复用信号 0: GPIO_10 (Default)<br>复用信号 1: PWM2<br>复用信号 2: ANTO_SW<br>复用信号 3: SPI0_CS0_N<br>复用信号 4: I2S_SCLK                                                  |

| 15  | GPIO_11 | I/O | 3.3/1.8 | 复用信号 0: GPIO_11 (Default)<br>复用信号 1: PWM3<br>复用信号 2: RADAR_ANTI_SW<br>复用信号 3: SPI0_IN<br>复用信号 4: I2S_LRCLK                                              |

| 16  | GPIO_12 | I/O | 3.3/1.8 | 复用信号 0: GPIO_12 (Default)                                                                                                                               |

| PIN | 管脚名称      | 类型  | 电压 (V)    | 说明                                                                                                            |

|-----|-----------|-----|-----------|---------------------------------------------------------------------------------------------------------------|

|     |           |     |           | 复用信号 1: PWM4<br>复用信号 2: ANT1_SW<br>复用信号 4: I2S_DI                                                             |

| 24  | GPIO_13   | I/O | 3.3/1.8   | 复用信号 0: GPIO_13 (Default)<br>复用信号 1: UART1_CTS<br>复用信号 2: RADAR_ANTO_SW<br>复用信号 3: 保留<br>复用信号 4: JTAG_TMS/SWD |

| 25  | GPIO_14   | I/O | 3.3/1.8   | 复用信号 0: GPIO_14 (Default)<br>复用信号 1: UART1_RTS<br>复用信号 2: RADAR_ANTI_SW<br>复用信号 3: 保留<br>复用信号 4: JTAG_TCK/SWC |

| 26  | UART1_T_X | OD  | 5/3.3/1.8 | 复用信号 0: GPIO_15<br>复用信号 1: UART1_TX<br>复用信号 2: I2C1_SDA                                                       |

| 27  | UART1_RX  | I   | 5/3.3/1.8 | 复用信号 0: GPIO_16<br>复用信号 1: UART1_RX<br>复用信号 2: I2C1_SCL                                                       |

## 1.2.11 CLK 管脚

CLK 管脚如表 1-12 所示。

表1-12 CLK 管脚

| PIN | 管脚名称 | 电压 (V) | 说明                           |

|-----|------|--------|------------------------------|

| 31  | XIN  | 1.6    | 晶体 XIN, 支持 24MHz 或 40MHz 晶体。 |

| PIN | 管脚名称 | 电压 (V) | 说明                            |

|-----|------|--------|-------------------------------|

| 32  | XOUT | 1.6    | 晶体 XOUT, 支持 24MHz 或 40MHz 晶体。 |

# 2 电性能参数

- 2.1 电流分布

- 2.2 极限工作条件

- 2.3 推荐工作条件

- 2.4 DC/AC 电气参数

- 2.5 上下电要求

## 2.1 电流分布

功耗分布如表 2-1 所示。

表2-1 电流参数

| 符号       | 描述         |         | 最小值 | 典型值 | 最大值 | 单位 |

|----------|------------|---------|-----|-----|-----|----|

| VBAT_IN  | VBAT_IN 电源 |         | -   | -   | 600 | mA |

| DVDD3318 | IO 输入电源    | BUCK 方案 | -   | -   | 110 | mA |

|          |            | LDO 方案  | -   | -   | 300 | mA |

## 2.2 极限工作条件

## 须知

极限工作电压参数如表 2-2 所示，超过这些数值，可能导致芯片损坏与可靠性问题。

芯片 ESD 防护能力如表 2-3

表2-2 极限工作电压参数

| 符号       | 描述           | 最小值  | 最大值  | 单位 |

|----------|--------------|------|------|----|

| VBAT_IN  | VBAT_IN 输入电源 | -0.3 | 5.5  | V  |

| DVDD3318 | IO 输入电源      | -0.3 | 3.63 | V  |

表2-3 芯片引脚 ESD 防护

| ESD 模型                              | 防护能力  |

|-------------------------------------|-------|

| ESD-CDM                             | 500V  |

| ESD-HBM                             | 2.5kV |

| ESD-HBM (UART0/UART1 耐 5V IO 对 GND) | 6kV   |

## 2.3 推荐工作条件

推荐工作条件如表 2-4 所示。

表2-4 推荐工作条件

| 符号       | 描述           | 最小值  | 典型值     | 最大值  | 单位 |

|----------|--------------|------|---------|------|----|

| VBAT_IN  | VBAT_IN 输入电源 | 3.0  | 3.3/5   | 5.25 | V  |

| DVDD3318 | IO 输入电源      | 1.62 | 1.8/3.3 | 3.63 | V  |

## 2.4 DC/AC 电气参数

表2-5 DC 电气参数表 (DVDD3318=1.8V GPIO 功能)

| 符号              | 描述      | 最小值             | 典型值   | 最大值             | 单位 |

|-----------------|---------|-----------------|-------|-----------------|----|

| DVDD3318        | 接口电压    | 1.62            | 1.8   | 1.98            | V  |

| V <sub>IH</sub> | 高电平输入电压 | 0.65 × DVDD3318 | -     | -               | V  |

| V <sub>IL</sub> | 低电平输入电压 | -0.3            | -     | 0.35 × DVDD3318 | V  |

| I <sub>L</sub>  | 输入漏电流   | -               | -     | 1.3             | μA |

| I <sub>OZ</sub> | 三态输出漏电流 | -               | -     | 3.8             | μA |

| V <sub>OH</sub> | 高电平输出电压 | 0.75 × DVDD3318 | -     | -               | V  |

| V <sub>OL</sub> | 低电平输出电压 | -               | -     | 0.25 × DVDD3318 | V  |

| R <sub>PU</sub> | 内部上拉电阻  | 25.18           | 30.11 | 35.73           | kΩ |

| R <sub>PD</sub> | 内部下拉电阻  | 23.57           | 28.0  | 32.82           | kΩ |

| I <sub>OH</sub> | 高电平输出电流 | 3.65            | 3.65  | 27.31           | mA |

| I <sub>OL</sub> | 低电平输出电流 | 3.46            | 3.46  | 27.55           | mA |

表2-6 DC 电气参数表 (DVDD3318=3.3V GPIO 功能)

| 符号              | 描述      | 最小值  | 典型值 | 最大值           | 单位 |

|-----------------|---------|------|-----|---------------|----|

| DVDD3318        | 接口电压    | 2.97 | 3.3 | 3.63          | V  |

| V <sub>IH</sub> | 高电平输入电压 | 2.0  | -   | DVDD3318 +0.3 | V  |

| V <sub>IL</sub> | 低电平输入电压 | -0.3 | -   | 0.8           | V  |

| I <sub>L</sub>  | 输入漏电流   | -    | -   | 2.0           | μA |

| I <sub>OZ</sub> | 三态输出漏电流 | -    | -   | 9.1           | μA |

| 符号       | 描述      | 最小值              | 典型值   | 最大值   | 单位 |

|----------|---------|------------------|-------|-------|----|

| $V_{OH}$ | 高电平输出电压 | DVDD3318<br>-0.2 | -     | -     | V  |

| $V_{OL}$ | 低电平输出电压 | -                | -     | 0.2   | V  |

| $R_{PU}$ | 内部上拉电阻  | 23.57            | 28.0  | 32.81 | kΩ |

| $R_{PD}$ | 内部下拉电阻  | 25.45            | 30.67 | 36.97 | kΩ |

| $I_{OH}$ | 高电平输出电流 | 3.98             | 3.98  | 29.87 | mA |

| $I_{OL}$ | 低电平输出电流 | 3.18             | 3.18  | 25.26 | mA |

表2-7 DC 电气参数表 (耐 5V GPIO, 即 UART/I2C 管脚)

| 符号        | 描述                                | 最小值  | 典型值   | 最大值                  | 单位 |

|-----------|-----------------------------------|------|-------|----------------------|----|

| $V_{IH}$  | 高电平输入电压                           | 1.5  | -     | -                    | V  |

| $V_{IL}$  | 低电平输入电压                           | -0.5 | -     | 0.8                  | V  |

| $V_{OL1}$ | 低电平输出电压 1                         | 0    | -     | 0.4                  | V  |

| $V_{OL2}$ | 低电平输出电压 2                         | 0    | -     | 0.2 × DVDD3318       | V  |

| $I_{OL}$  | 低电平输出电流                           | -    | 4.485 | -                    | mA |

| $T_{of}$  | $V_{ihmin}$ 到 $V_{ilmax}$ 的输出下降时间 | 250  | -     | 20 × (DVDD3318/5.5V) | ns |

| $T_{sp}$  | 输入滤波器必须抑制的尖峰脉冲宽度                  | 0    | -     | 50                   | ns |

| $I_i$     | 每个 IO 引脚的输入电流                     | -10  | -     | 10                   | μA |

| $C_i$     | 每个 IO 引脚的电容                       | -    | -     | 10                   | pF |

### 说明

- 耐 5V GPIO 输出管脚类型为 OD 管脚，输出高电平跟随上拉电压，支持 1.8V/3.3V/5V 上拉。

## 2.5 上下电要求

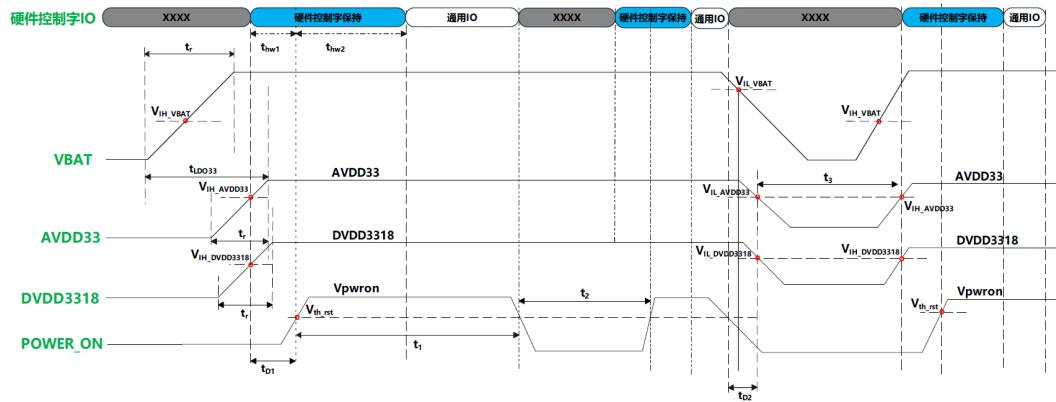

图2-1 上电顺序图

### 说明

- 上下电边沿要单调、无回沟。

- 请严格按照上下电时序规格进行硬件设计，如果不满足约束，建议硬件设计方案增加复位芯片。

- VBAT 对应管脚：VBAT\_IN。

- AVDD33 对应管脚：AVDD33\_RF0、AVDD33\_RF1、AVDD33\_RF2、AVDD33\_0、AVDD33\_1、BUCK\_IN。

- DVDD3318 对应管脚：DVDD3318。

表2-8 时间参数说明

| 参数    | 描述                                                           | 说明          | 最小值<br>(min) | 最大值<br>(max) | 单位 |

|-------|--------------------------------------------------------------|-------------|--------------|--------------|----|

| $t_1$ | 上电后，PWR_ON 的高电平持续时间                                          | -           | 20           | -            | ms |

| $t_2$ | 睡眠后，唤醒的间隔时间<br>(AVDD33 和 DVDD3318 为高电平时，PWR_ON 拉低后再次拉高的间隔时间) | 推荐间隔大于 20ms | 5            | -            | ms |

| $t_3$ | 下电后，再次上电的间隔时间                                                | -           | 50           | -            | ms |

| 参数         | 描述                                  | 说明                                                     | 最小值<br>(min) | 最大值<br>(max) | 单位 |

|------------|-------------------------------------|--------------------------------------------------------|--------------|--------------|----|

| $t_{D1}$   | 上电时, PWR_ON 相对电源上电的延时时间;            | 上电时,<br>PWR_ON 晚于<br>AVDD33 和<br>DVDD3318 上<br>电较晚者;   | 1            | -            | ms |

| $t_{D2}^1$ | 下电时, PWR_ON 相对电源下电的提前时间。            | 下电时,<br>PWR_ON 不晚<br>于 AVDD33 和<br>DVDD3318 下<br>电较早者。 | 0            | -            | ms |

| $t_{hw1}$  | 上电时, 硬件配置字 IO 在 PWR_ON 拉高前的电平建立时间   | -                                                      | 1            | -            | ms |

| $t_{hw2}$  | 上电时, 硬件配置字 IO 在 POWER_ON 拉高后的电平保持时间 | -                                                      | 10           | -            | ms |

| $t_r$      | 电源上升时间                              | -                                                      | 1            | 10           | ms |

注 1: PWR\_ON 与 DVDD3318 合并控制时, PWR\_ON 跟随 DVDD3318 启动, 板级需要增加 RC 延时电路, 下电场景 PWR\_ON 跟随 DVDD3318 下电; PWR\_ON 与 DVDD3318 独立控制时, 下电场景 PWR\_ON 下电不晚于 DVDD3318 和 AVDD33。

表2-9 电压参数说明

| 参数             | 描述                                          | 阈值  | 单位 |

|----------------|---------------------------------------------|-----|----|

| $V_{th\_rst}$  | PWR_ON 的上升/下降沿电平, 芯片内<br>部 PMU 的复位及解复位电压阈值。 | 1.4 | V  |

| $V_{lh\_vbat}$ | AVDD33 的上电阈值电平, LDO33 开始<br>上电              | 2.3 | V  |

| $V_{ll\_vbat}$ | AVDD33 的下电阈值电平, LDO33 开始                    | 3.4 | V  |

| 参数                 | 描述                  | 阈值                    | 单位 |

|--------------------|---------------------|-----------------------|----|

|                    | 下电                  |                       |    |

| $V_{IH\_AVDD33}$   | AVDD33 的上电阈值电平      | 2.3                   | V  |

| $V_{IL\_AVDD33}$   | AVDD33 的下电阈值电平      | 2.3                   | V  |

| $V_{IH\_DVDD3318}$ | DVDD3318 的上电阈值电平    | $0.8 \times DVDD3318$ | V  |

| $V_{IL\_DVDD3318}$ | DVDD3318 的下电阈值电平    | $0.8 \times DVDD3318$ | V  |

| $V_{pwron}$        | 芯片上电后 PWR_ON 稳态保持电平 | 1.6                   | V  |

| AVDD33             | 芯片模拟模块供电电源          | 3.3                   | V  |

| DVDD3318           | 芯片数字模块供电电源          | 3.3 / 1.8             | V  |

### 上电时序说明：

1. 电源 VBAT/DVDD3318 电源上电时间范围建议1ms~10ms（VBAT 支持上电时间最快200μs）。

2. VBAT 支持 5V/3.3V，若芯片采用 5V\_BUCK 方案，则 AVDD33 由芯片内部 LDO33 产生，上电时间  $t_{LDO33}$ （VBAT 开启上电到 LDO33 输出 3.3V 的时间）跟随 VBAT 上电时间变化；VBAT<1ms 上电，则  $t_{LDO33} = 1\text{ms}$ ；VBAT<10ms 上电，则  $t_{LDO33} = 10\text{ms}$ 。

3. 电源 VBAT、AVDD33、DVDD3318 间上电顺序无要求，上电完成 1ms 后将 PWR\_ON 上拉至高电平（DVDD3318）。当确保 PWR\_ON 晚于 DVDD3318 和 AVDD33 电源 1ms（即  $T_{pwron1} \geq 1\text{ms}$ ）后，上电达到 1.4V ( $V_{th\_rst}$ ) 时，才可确保芯片正常工作。

4. 电源上电后，在 PWR\_ON 拉高前，硬件控制字 IO 需要提前维持至少 1ms， $t_{hw1} \geq 1\text{ms}$ ；在 PWR\_ON 拉高后，硬件控制字 IO 需要持续维持至少 10ms， $t_{hw2} \geq 10\text{ms}$ 。

5. WS63 系列芯片内部 PMU 检测到 PWR\_ON 信号为高电平 400us 后，芯片内部开始解复位流程，有序地开启各电源，解复位时间为 21ms，其中硬件配置字在解复位之后 9.5ms 内锁存，然后芯片正常工作。

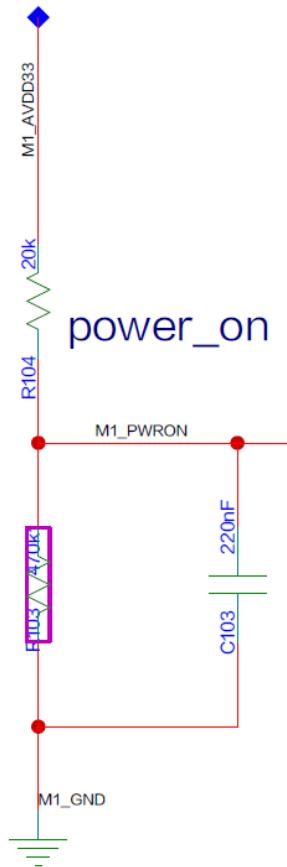

6. 对于 DVDD3318 和 AVDD33 电源同源、PWR\_ON 跟随 DVDD3318 启动的情况，无法满足  $T_{pwron} \geq \text{ms}$  要求，可以采用板级加 RC 延时电路解决，RC 常数要大于等于  $20\text{k} \times 220\text{nF} = 4.4\text{ms} \approx 5\text{ms}$ 。

下电时序说明：

1. 当电源 VBAT\_IN、AVDD33、DVDD3318 正常供电，通过拉低 PWR\_ON 管脚控制芯片复位时，PWR\_ON 电压要低于 1.4V 才能重新拉高启动芯片。

2. 当芯片整体掉电时，需要保证 VBAT\_IN、AVDD33、DVDD3318 和 PWR\_ON 电压残压低于 800mV，才能重新上电（重新上电需要满足上电时序要求）。

3. 芯片 VBAT 采用 5V 方案时，VBAT 小于 3.4V，LDO33 输出的 3.3V 开始掉电。

**注意**

硬件设计时，请严格遵循上述上下电时序约束。如果应用场景无法满足芯片上下电规格要求，例如电源上电时序慢、供电电压不稳定及快速上下电等场景，建议硬件方案增加复位芯片设计，监测芯片 3V3 电压并控制 PWR\_ON，保障芯片正常运行。详细请查看《WS63 硬件模组参考设计》。

# 3 原理图设计建议

- 3.1 小系统设计建议

- 3.2 电源参考设计

- 3.3 外围接口设计建议

- 3.4 控制信号应用参考设计

- 3.5 RFIO 设计

- 3.6 RFI 设计

## 3.1 小系统设计建议

WS63V100 系列芯片内部集成自研 CPU，小系统指芯片电路能够正常工作的最小外围电路配置，此部分的电路主要包括：时钟电路、复位电路。

### 3.1.1 时钟参考设计

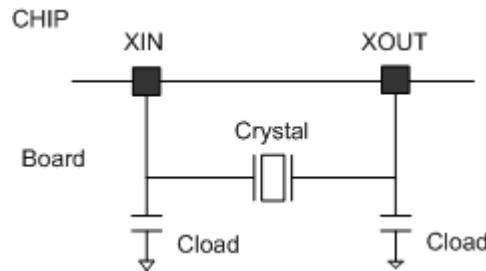

CPU 支持的晶体时钟 24MHz/40MHz，在使用外部晶体时，电路结构如图 3-1 所示。硬件设计时，时钟管脚靠近芯片端预留 0Ω 电阻串位，当晶体与 RF 隔离度不满足要求时，可通过串接电感改善隔离度。

图3-1 使用 Crystal 输入参考时钟的参考电路图

WS63 系列芯片时钟电路外部 Crystal 电气特性的要求如表 3-1 和表 3-2 所示。

表3-1 40MCrystal 电气特性要求

| 参数          | 符号    | 晶体选型规格    |         |         | 单位  | 说明                                                  |

|-------------|-------|-----------|---------|---------|-----|-----------------------------------------------------|

| 标称频率        | f     | 40        | 40      | 40      | MHz | -                                                   |

| 负载电容        | CL    | 8         | 9       | 10      | pF  | -                                                   |

| 频率容差        | f_tol | ±10       | ±10     | ±10     | ppm | 晶体初始频偏                                              |

| 等效电阻        | ESR   | ≤50       | ≤40     | ≤35     | Ohm | 影响起振                                                |

| 动态电容        | C1    | ≥2.8      | ≥3.4    | ≥4      | fF  | 影响频率校准                                              |

| 静态电容        | C0    | ≤3        | ≤3      | ≤3      | pF  | -                                                   |

| 激励功率        | DL    | ≥150      | ≥150    | ≥150    | uW  | -                                                   |

| 工作温度        | T     | -40~85    | -40~85  | -40~85  | °C  | -                                                   |

| 板级负载电容 (单端) | CL1   | 2.2 (参考值) | 4 (参考值) | 6 (参考值) | pF  | 需根据板级寄生、封装寄生电容调整。<br>8pF CL1 可选, 9pF/10pF CL1 必须上件。 |

表3-2 24MCrystal 电气特性要求

| 参数             | 符号    | 晶体选型规格    | 单位  | 备注                              |

|----------------|-------|-----------|-----|---------------------------------|

| 标称频率           | f     | 24        | MHz | -                               |

| 负载电容           | CL    | 8         | pF  | -                               |

| 频率容差           | f_tol | ±10       | ppm | 晶体初始频偏                          |

| 等效电阻           | ESR   | ≤100      | Ohm | -                               |

| 动态电容           | C1    | ≥3        | fF  | -                               |

| 静态电容           | C0    | ≤3        | pF  | -                               |

| 工作温度           | T     | -40~85    | °C  | -                               |

| 激励功率           | DL    | ≥150      | μW  | -                               |

| 板级负载电容<br>(单端) | CL1   | 2.2 (参考值) | pF  | 根据板级寄生、封装<br>寄生电容调整。<br>CL1 可选。 |

CL1 实际调测步骤如下 (需要使用综测仪进行测试, 综测仪可以直接测试出频偏):

步骤 1 8pF 默认板级无负载电容 CL0=0; 9pF 默认 xin 与 xou 上件 2pF, CL0=2; 10pF 默认 xin 与 xou 上件 4pF, CL0=4。

- 配置频偏校准粗调码值 xo\_trim\_coarse=0, 频偏校准细调码值 xo\_trim\_fine=0, 记录此时频偏为 fmax。

- 配置频偏校准粗调码值 xo\_trim\_coarse=15, 频偏校准细调码值 xo\_trim\_fine=127, 记录此时频偏为 fmin。

步骤 2 若  $f_{max} \geq 35ppm$  且  $f_{min} \leq -35ppm$ , 则不需要增加 CL1, 调测结束; 若不满足, 则进行步骤 3~步骤 7。

步骤 3 板级负载电容根据 CL=8pF/9pF/10pF 分别在 xin 与 xout 上件 1pF/2pF/4pF; 配置频偏校准粗调码值 xo\_trim\_coarse=0, 频偏校准细调码值 xo\_trim\_fine=0, 记录此时频偏为 f0 (此时 CL=9pF/10pF 的 f0 即为第一步的 fmax)。

步骤 4 板级负载电容在第 2 步的基础上增大 1pF，根据  $CL=8pF/9pF/10pF$  分别在  $xin$  与  $xout$  上件  $2pF/3pF/5pF$ ；配置频偏校准粗调码值  $xo\_trim\_coarse=0$ ，频偏校准细调码值  $xo\_trim\_fine=0$ ，记录此时频偏为  $f1$ 。

步骤 5 此时得到频偏调节率  $ratio\_adjust=(f1-f0)/1pF$ ，则进一步可以计算可以得到  $CL1=(fmax+fmin)/2/ratio\_adjust+CL0$ 。

步骤 6 将得到的  $CL1$  分别在  $xin$  与  $xout$  上件，此时测得  $fmax \approx fmin$ ，此时  $CL1$  为最佳值。

步骤 7 为保证测试准确，推荐测试 3pcs 单板来保证一致性。

#### ----结束

以  $CL=8pF$  为例，如表 3-3 所示。

表3-3 CL1 测试举例

| 晶体 CL                                                      | $xin$ 与 $xout$ 上件容值 | $xo\_trim\_coarse$ | $xo\_trim\_fine$ | $fmax$ | $fmin$ | $f0$  | $f1$  |

|------------------------------------------------------------|---------------------|--------------------|------------------|--------|--------|-------|-------|

| 8pF                                                        | 0                   | 0                  | 0                | 100ppm | -      | -     | -     |

|                                                            | 0                   | 15                 | 127              | -      | -20ppm | -     | -     |

|                                                            | 1pF                 | 0                  | 0                | -      | -      | 90ppm | -     |

|                                                            | 2pF                 | 0                  | 0                | -      | -      | -     | 80ppm |

| 此时 $ratio\_adjust=10ppm/1pF$ , $CL1= (100-20) /2/10+0=4pF$ |                     |                    |                  |        |        |       |       |

| 8pF                                                        | 4pF                 | 0                  | 0                | 60ppm  | -      | -     | -     |

|                                                            | 4pF                 | 15                 | 127              | -      | -60ppm | -     | -     |

#### □ 说明

配置频偏校准粗调码值与细调码值命令详细说明请参见《WS63V100 产线工装用户指南》。

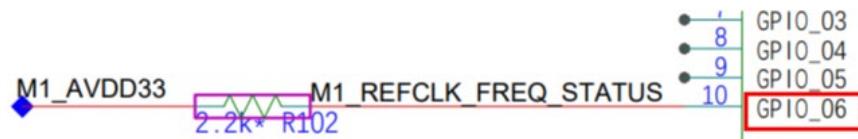

WS63 系列芯片支持 24MHz、40MHz 参考时钟频率。参考时钟频率通过 GPIO\_06 的硬件配置字进行判断，上电时通过读取 GPIO\_06 高低电平选择内部分频系数。外部时钟选择真值如表 3-4 所示。

表3-4 外部时钟选择真值表

| 时钟频率 | REFCLK_FREQ_STATUS | 说明 |

|------|--------------------|----|

|------|--------------------|----|

| 时钟频率  | REFCLK_FREQ_STATUS | 说明                   |

|-------|--------------------|----------------------|

| 40MHz | 0                  | 默认内部下拉。              |

| 24MHz | 1                  | 上拉 2.2kΩ 到 DVDD3318。 |

图3-2 频率选择管脚参考电路图

### 3.1.2 复位电路

WS63V100 系列芯片集成内部 POR (Power On Reset) 电路以及 Watchdog, PWR\_ON 管脚为芯片复位管脚, 低电平使能。PWR\_ON 上电必须要晚于 AVDD33 和 DVDD3318 电源 1ms, 建议在 PWR\_ON 管脚增加 RC 延时电路, 例如  $R=20\text{k}\Omega$ ,  $C=220\text{nF}$ , RC 参数约为 4.4ms。

图3-3 PWR\_ON 电路设计参考

### 说明

硬件设计时，power\_on 管脚建议上件 RC 延时电路，根据电源上电响应速度，调节 RC 参数，保证上电时序满足芯片规格约束；同时预留下拉电阻位置，作为下电快速泄放通道和 power\_on 分压控制电路使用。

### 3.1.3 硬件初始化系统配置电路

WS63V100 系列芯片的 PIN23 为电源方案配置管脚，当 VBAT 电源选择 3V3 方案时，PIN23 需跟随电源启动拉高。芯片 PIN7、8、10 为硬件配置字，PIN5、13、15 为芯片保留的硬件配置字，硬件配置字管脚在芯片内部默认有  $28k\Omega$  左右的下拉电阻。芯片上电初始化时会检测 6 个硬件配置字引脚的电平状态，以进入不同的工作模式，详情见表 3-5，使用时必须注意芯片上电初始化时的引脚初始输入电平。若需通过上拉电阻将硬件配置字上电初始化时设置为高电平，PIN7、PIN8、PIN10 建议通过  $2.2k\Omega$  电阻上拉到 DVDD3318。

表3-5 硬件配置字信号描述

| 信号名 | PIN | 管脚电平 | 芯片工作模式 |

|-----|-----|------|--------|

|-----|-----|------|--------|

| 信号名                             | PIN     | 管脚电平  | 芯片工作模式       |

|---------------------------------|---------|-------|--------------|

| FLASH BOOT (GPIO_03)            | 7       | 0     | 正常启动         |

|                                 |         | 1     | 进烧录模式        |

| JTAG_ENABLE (GPIO_04)           | 8       | 0     | 正常启动         |

|                                 |         | 1     | 使能 JTAG 调试接口 |

| REFCLK_FREQ_STATUS (GPIO_06)    | 10      | 0     | 时钟选择 40MHz   |

|                                 |         | 1     | 时钟选择 24MHz   |

| 保留 1 (GPIO_01)                  | 5       | 0     | 正常工作模式       |

|                                 |         | 1     | 禁止           |

| 保留 2 (GPIO_11) : 保留 3 (GPIO_09) | 15 : 13 | 0 : 0 | 正常工作模式       |

|                                 |         | 0 : 1 | 正常工作模式       |

|                                 |         | 1 : 0 | 正常工作模式       |

|                                 |         | 1 : 1 | 禁止           |

注：1. 上电初始化时，硬件配置字 JTAG\_ENABLE 高电平使能后，GPIO13 和 GPIO14 固定使用为 JTAG 接口。

2. 上电初始化时，硬件配置字 FLASH\_BOOT 高电平使能后，芯片启动流程会停留在 BOOT 阶段，等待烧录。

表3-6 电源方案选择管脚说明

| 信号名     | PIN | 管脚电平 | 芯片工作模式             |

|---------|-----|------|--------------------|

| PWR_SEL | 23  | 0    | VBAT_IN 采用 5V 供电。  |

|         |     | 1    | VBAT_IN 采用 3V3 供电。 |

**须知**

- 特别注意：不要使硬件配置字进入表 3-5 中所描述的禁用状态。

- 芯片使用时，必须注意在上电初始化过程中 PIN5、7、8、10、13、15 所有的 6 个硬件配置字管脚的电平状态（包含对端芯片及器件以及板级上下拉电阻对硬件配置字管脚上电初始化电平的影响）。

- 芯片保留的硬件配置字管脚 PIN5、13、15，硬件设计时相应管脚禁止加上拉电阻。

- 上电过程中硬件配置字详细的时序约束请参考图 2-1。

- 芯片上电过程中，在 PWR\_ON 管脚拉高前至少 1ms，拉高后至少 10ms 的时间内，需要保证所有硬件配置字管脚电平状态稳定不变；

- 由于硬件配置字管脚对上电时序有约束，所以不建议作为功能 IO 使用，以避免初始化时电平识别错误从而导致功能异常；

- 如果基于设计需求，需要将硬件配置字管脚做 IO 使用，注意引脚上电初始化电平是否满足芯片启动要求，以及默认上下拉电阻所带来的影响。

## 3.2 电源参考设计

**说明**

系统电源的设计，详细请参见 WS63 原理图。

### 3.2.1 电源方案

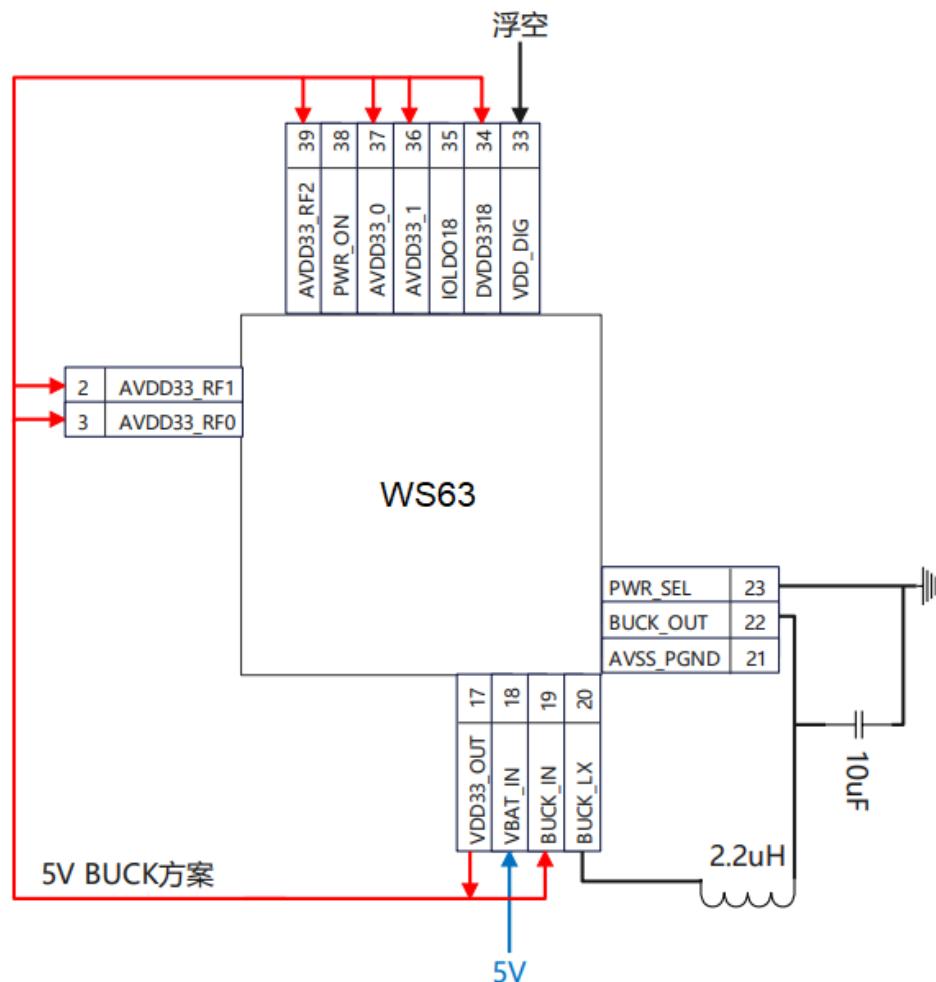

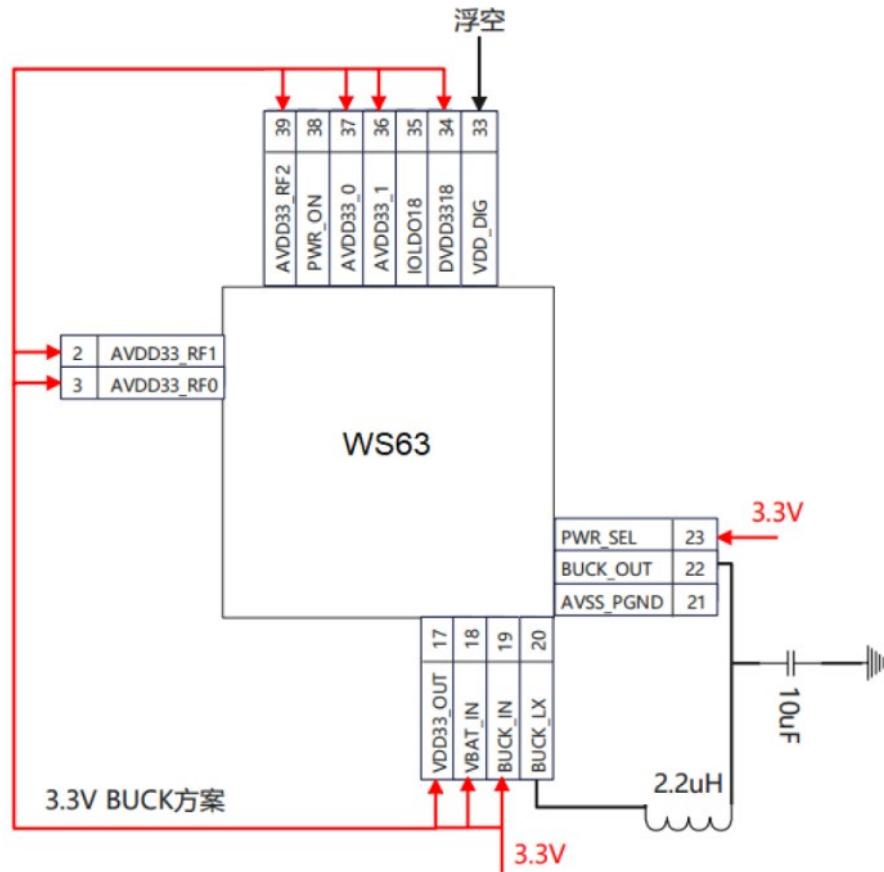

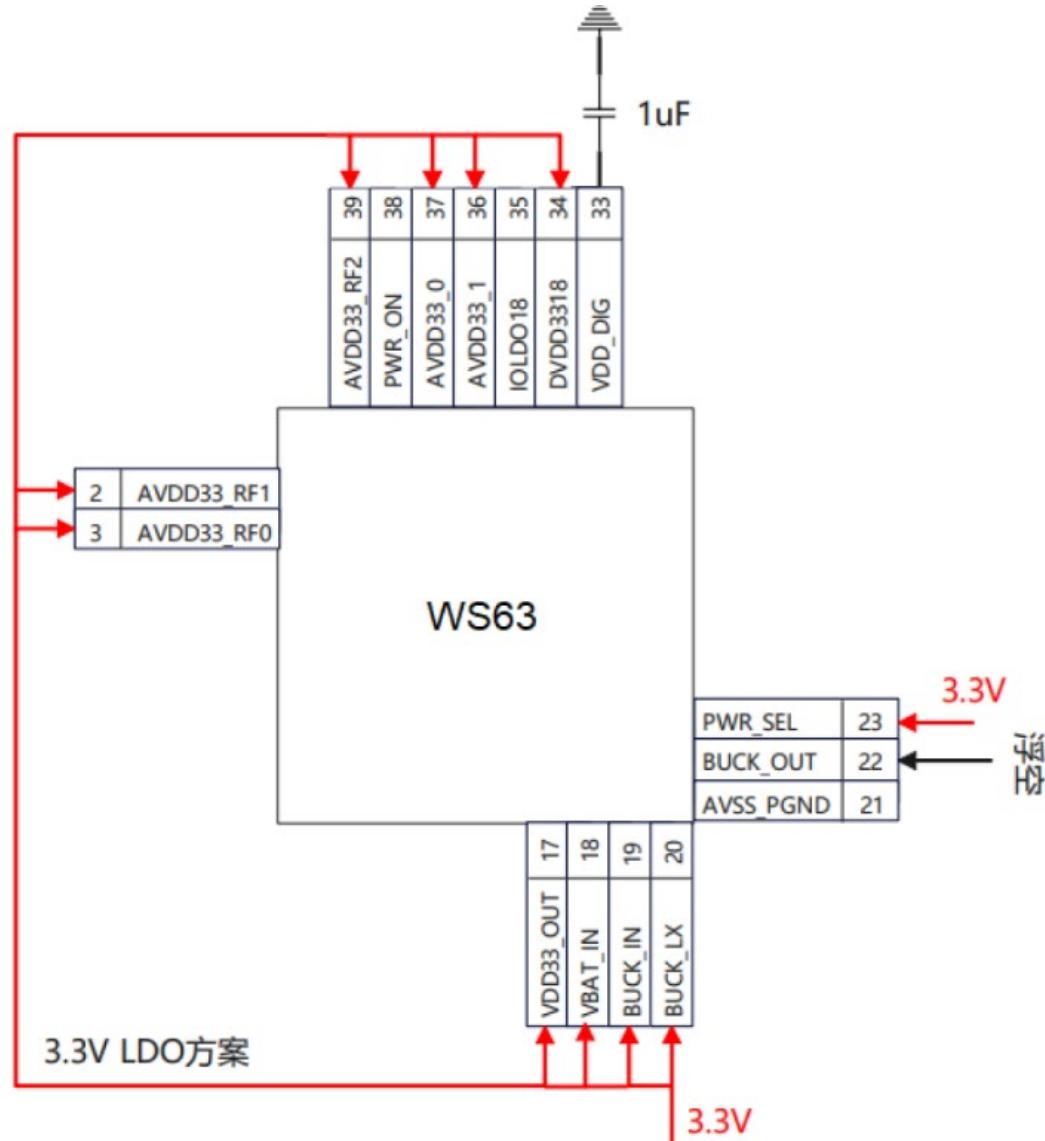

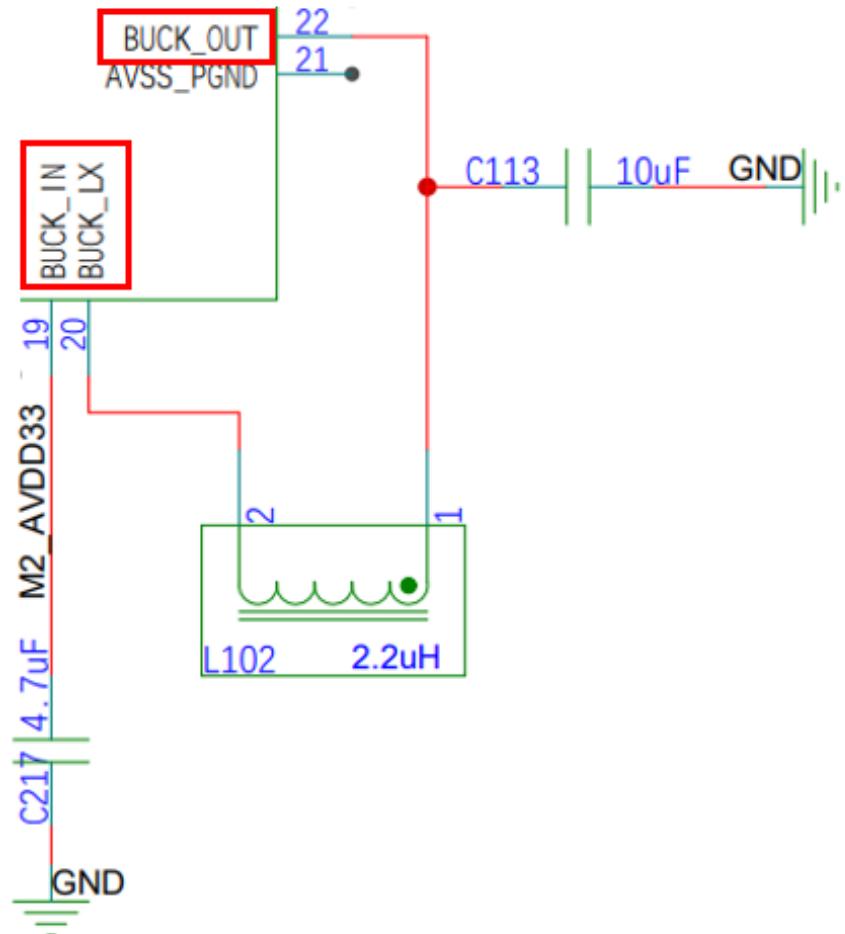

WS63 系列芯片共有 3 种芯片电源方案，分别为 5V BUCK 方案，3.3V BUCK 方案，3.3V LDO 方案，因此在不同电源方案芯片引脚及外围电路存在差异。

- 方案一：5V BUCK 方案。BUCK\_LX 连接板级 2.2uH 电感，然后连接到 BUCK\_OUT；BUCK\_OUT 近端添加 10uF 电容；VDD\_DIG 管脚浮空；PWR\_SEL 管脚接地。VBAT\_IN 接 5V 板级输入电压；VDD33\_OUT 输出 3.3V，通过硬件连接到 BUCK\_IN 及整芯片需要 3.3V 电压的管脚。

- 方案二：3.3V BUCK 方案。BUCK\_LX 连接板级 2.2uH 电感，然后连接到 BUCK\_OUT；BUCK\_OUT 近端添加 10uF 电容；VDD\_DIG 管脚浮空；PWR\_SEL 管脚接 3.3V。VBAT\_IN 接 3.3V 板级输入电压；VDD33\_OUT、BUCK\_IN 接板级 3.3V。

- 方案三：3.3V LDO 方案。BUCK\_LX 连接板级 3.3V 电压；BUCK\_OUT 管脚浮空；VDD\_DIG 近端添加 1uF 电容；PWR\_SEL 管脚接 3.3V。VBAT\_IN 接 3.3V 板级输入电压；VDD33\_OUT、BUCK\_IN 接板级 3.3V。

WS63 系列芯片 3 种电源方案示意如图 3-4、图 3-5 和图 3-6 所示。

图3-4 WS63 系列芯片 5V BUCK 方案

图3-5 WS63 系列芯片 3.3V BUCK 方案

图3-6 WS63 系列芯片 3.3V LDO 方案

### 说明

1. 硬件方案设计时，推荐采用 3V3\_BUCK 供电方案，实现更好的性能表现。5V\_BUCK 方案和 3V3\_LDO 方案仅建议在低功耗场景下采用，且应用场景中芯片位置板温建议不超过 70°C。

2. 电源管脚 DVDD3318 支持 3.3V 或 1.8V 供电。当 DVDD3318 采用 1.8V 供电时，硬件设计上需要将 PIN35 (IOLDO18) 和 PIN34 (DVDD3318) 短接，由外部提供 1.8V 电压。

## 3.2.2 电源规格

需要的外部电源包括：

- 供电电源 VBAT\_IN

- IO 电源 DVDD3318

推荐工作条件如表 3-7 所示。

表3-7 推荐工作条件

| 符号         | PIN 序号 | 说明                    | 最小值 (V) | 典型值 (V) | 最大值 (V) | 电压精度 DC+AC | PCB 布线参考电流值 (mA) (仅供布线参考) |

|------------|--------|-----------------------|---------|---------|---------|------------|---------------------------|

| AVDD33_RF1 | 2      | 由外部电源提供。              | 3.0     | 3.3     | 3.6     | ±5%        | 400                       |

| AVDD33_RF0 | 3      | 由外部电源提供。              | 3.0     | 3.3     | 3.6     | ±5%        | 100                       |

| AVDD33_RF2 | 39     | 由外部电源提供。              | 3.0     | 3.3     | 3.6     | ±5%        | 100                       |

| AVDD33_0   | 37     | AVDD33 供电电源, 由外部电源提供。 | 3.0     | 3.3     | 3.6     | ±5%        | 50                        |

| AVDD33_1   | 36     | 由外部电源提供。              | 3.0     | 3.3     | 3.6     | ±5%        | 140                       |

| IOLDO18    | 35     | 内部 LDO_DECAP, 外置 1μF。 | -       | 1.8     | -       | ±5%        | 200                       |

| DVDD3318   | 34     | IO 电源, 由外部电源提供。       | 1.62    | 1.8/3.3 | 3.63    | ±5%        | 300                       |

| VDD_DIG    | 33     | 内部 LDO_DECAP, 外置 1μF。 | -       | 0.9     | -       | ±5%        | 250                       |

| BUCK_OUT   | 22     | 内部数字电源输出              | -       | 0.9     | -       | ±5%        | 250                       |

| 符号        | PIN 序号 | 说明                              | 最小值 (V) | 典型值 (V) | 最大值 (V) | 电压精度 DC+AC | PCB 布线参考电流值 (mA) (仅供布线参考) |

|-----------|--------|---------------------------------|---------|---------|---------|------------|---------------------------|

|           |        | 出, 外置 $10\mu F$ 。               |         |         |         |            |                           |

| BUCK_IN   | 19     | 内部数字电源输入, 外置 $4.7\mu F$ 。       | 3.0     | 3.3     | 3.6     | $\pm 5\%$  | 100                       |

| VBAT_IN   | 18     | 芯片供电电源, 由外部电源提供, 外置 $10\mu F$ 。 | 3.0     | 3.3/5   | 5.25    | $\pm 5\%$  | 500                       |

| VDD33_OUT | 17     | 内部数字电源输出, 外置 $4.7\mu F$ 。       | 3.0     | 3.3     | 3.6     | $\pm 5\%$  | 500                       |

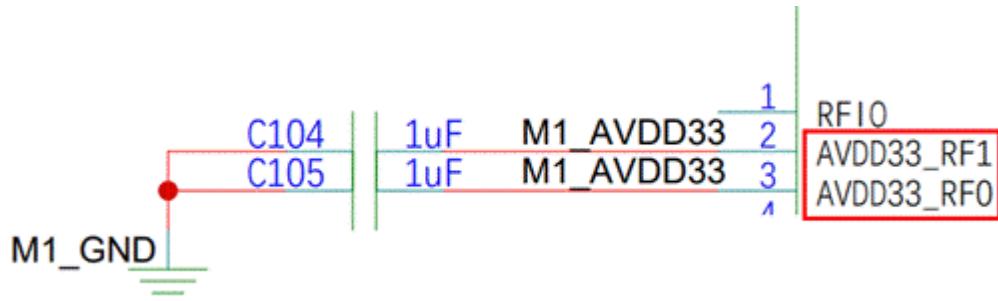

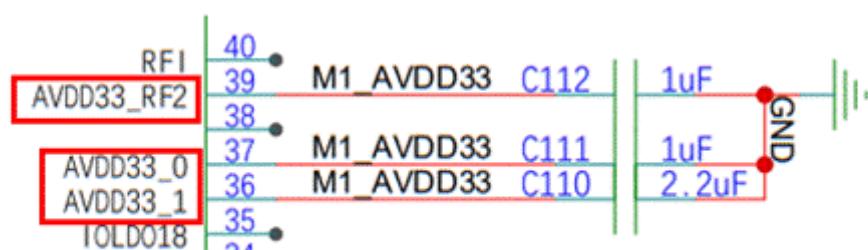

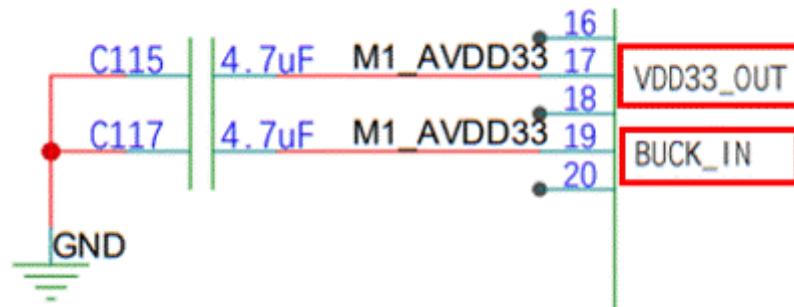

### 3.2.3 AVDD33 电源

WS63V100 系列芯片包含 6 个 AVDD33 电源输入管脚:

- AVDD33\_RF0、AVDD33\_RF1、AVDD33\_RF2: 芯片 RF 模块供电, 由外部提供。

- AVDD33\_0、AVDD33\_1: 电源 AVDD33, 由外部提供。

- BUCK\_IN: 内部 BUCK 电源输入, 由外部提供。

AVDD33 支持  $3.0V \sim 3.6V$  输入, 要求供电电源纹波及噪声峰峰值在  $\pm 5\%$  以内。

AVDD33 的每个电源输入管脚需要选择合适的去耦电容, 参考表 3-8 所示。

表3-8 AVDD33 电源管脚去耦电容

| 名称 | 设计建议 |

|----|------|

|    |      |

| 名称         | 设计建议                                |

|------------|-------------------------------------|

| AVDD33_RF1 | 外接 $1\mu F$ 电容, 耐压值 $\geq 6.3V$ 。   |

| AVDD33_RF0 | 外接 $1\mu F$ 电容, 耐压值 $\geq 6.3V$ 。   |

| AVDD33_RF2 | 外接 $1\mu F$ 电容, 耐压值 $\geq 6.3V$ 。   |

| AVDD33_0   | 外接 $1\mu F$ 电容, 耐压值 $\geq 6.3V$ 。   |

| AVDD33_1   | 外接 $2.2\mu F$ 电容, 耐压值 $\geq 6.3V$ 。 |

| BUCK_IN    | 外接 $4.7\mu F$ 电容, 耐压值 $\geq 6.3V$ 。 |

| VDD33_OUT  | 外接 $4.7\mu F$ 电容, 耐压值 $\geq 6.3V$ 。 |

图3-7 WS63V100 AVDD33 输入电路 1

图3-8 WS63V100 AVDD33 输入电路 2

图3-9 WS63V100 AVDD33 输入电路 3

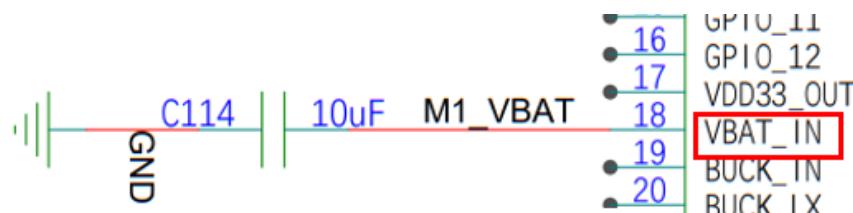

### 3.2.4 VBAT\_IN 电源

VBAT\_IN 给芯片提供工作电源，支持 3.3V 或 5V 输入，VBAT\_IN 电源可以由外部 PMU 芯片或者外部 BUCK 电路生成提供。推荐设计建议如表 3-9 所示，参考电路如图 3-10 所示。

表3-9 VBAT\_IN 电源设计建议

| 名称      | 设计建议                |

|---------|---------------------|

| VBAT_IN | 外接 10μF 电容，耐压值≥10V。 |

图3-10 VBAT\_IN 输入电路

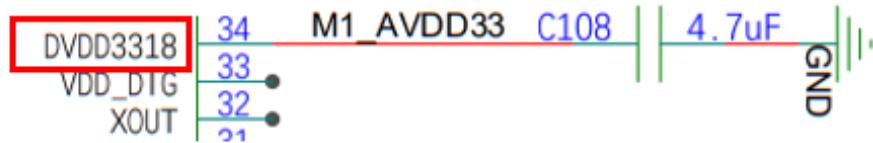

### 3.2.5 DVDD3318 电源

WS63V100 系列芯片包含 1 个 DVDD3318 电源输入管脚：

DVDD3318：支持 1.8V/3.3V 电压，推荐设计建议如表 3-10 所示，参考电路图如图 3-11 所示。

表3-10 DVDD3318 电源设计建议

| 名称       | 设计建议                                |

|----------|-------------------------------------|

| DVDD3318 | 外接 $4.7\mu F$ 电容, 耐压值 $\geq 6.3V$ 。 |

图3-11 DVDD3318 输入电路

### 说明

当 DVDD3318 选择 1V8 电源供电时, 需要将 DVDD3318 和 IOLDO18 短接, 即 PIN34 和 PIN35 短接。选择 3V3 电源供电时不需要。

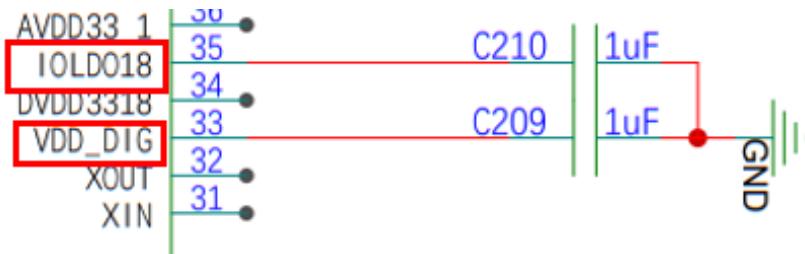

## 3.2.6 内部电源滤波电路

内部电源中的 IOLDO18、VDD\_DIG 需要外接滤波电容, 推荐设计建议如表 3-11 所示, 参考电路如图 3-12 所示。

表3-11 内部电源滤波电路设计建议

| 名称      | 设计建议                                               |

|---------|----------------------------------------------------|

| IOLDO18 | 内部 LDO_DECAP, 外接 $1\mu F$ 滤波电容。                    |

| VDD_DIG | 内部 LDO_DECAP, LDO 电源方案外接 $1\mu F$ 滤波电容, BUCK 方案悬空。 |

图3-12 内部电源滤波电路

### 3.2.7 BUCK 电源

VDD\_DIG 可以由内部 BUCK 生成或由内部 LDO 电源提供。参考电路如图 3-13 所示

表3-12 BUCK 电源设计建议

| 名称       | 设计建议                                     |

|----------|------------------------------------------|

| BUCK_LX  | BUCK LX 输出，外接 $2.2\mu\text{H}$ 电感。       |

| BUCK_IN  | 电压输入，给内部 LDO 等供电，外接 $4.7\mu\text{F}$ 电容。 |

| BUCK_OUT | 给芯片内部 LDO 供电，外接 $10\mu\text{F}$ 电容。      |

图3-13 BUCK 电源参考电路

### 说明

BUCK 电感推荐约束条件:

- 电感值  $2.2\mu\text{H}$ ,  $\pm 20\%$ 。

- 直流电阻 ( $R_{dc}$ )  $\leq 0.5\Omega$ 。

- 饱和电流  $\geq 1\text{A}$ 。

- $R_{dc}$  增大会导致功耗增加, 效率变低。

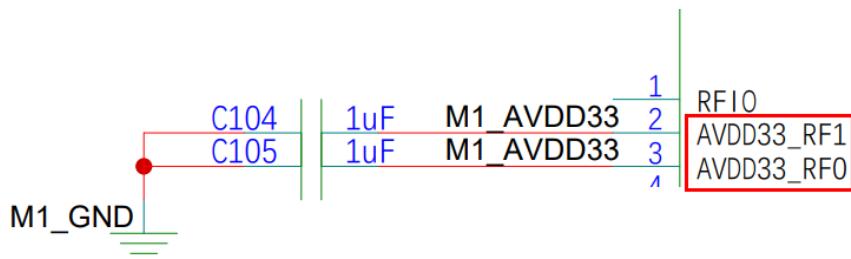

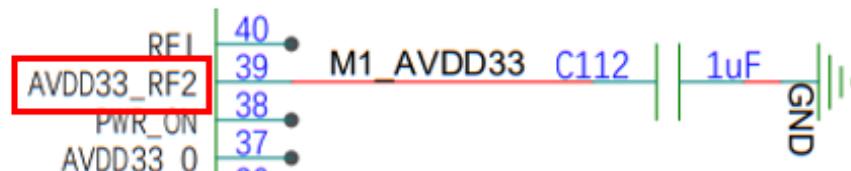

## 3.2.8 RF 电源

外部提供 RF 电源供电, 可与 AVDD33 电源接在一起, 设计建议如表 3-13 所示, 参考电路如图 3-14 和图 3-15 所示。

表3-13 RF 供电设计建议

| 名称         | 设计建议                  |

|------------|-----------------------|

| AVDD33_RF0 | AVDD33 供电, 外接 1μF 电容。 |

| AVDD33_RF1 | AVDD33 供电, 外接 1μF 电容。 |

| AVDD33_RF2 | AVDD33 供电, 外接 1μF 电容。 |

图3-14 RF 供电电路设计参考 1

图3-15 RF 供电电路设计参考 2

### 3.2.9 注意事项

TBD

## 3.3 外围接口设计建议

### 3.3.1 UART 接口

WS63V100 系列芯片支持三组 UART 接口，UART0 用于芯片烧录、维测、打印。

UART1、UART2 用于与其他设备对接，UART1 也可作为业务调试接口。设计建议如表 3-14 所示。硬件设计时引出 UART0、UART1 测试点，可以方便芯片业务功能调测。

表3-14 UART 接口设计建议

| 名称        | 设计建议                             |

|-----------|----------------------------------|

| UART0_RXD | 直连，走线≤5inch。                     |

| UART0_TXD | 直连，走线≤5inch。总线需要上拉，建议上拉电阻 2.2kΩ。 |

| UART1_TXD | 直连，走线≤5inch。总线需要上拉，建议上拉电阻 2.2kΩ。 |

| UART1_RXD | 直连，走线≤5inch。                     |

| UART1_RTS | 直连，走线≤5inch。                     |

| UART1_CTS | 直连，走线≤5inch。                     |

| UART2_TXD | 直连，走线≤5inch。                     |

| UART2_RXD | 直连，走线≤5inch。                     |

| UART2_RTS | 直连，走线≤5inch。                     |

| UART2_CTS | 直连，走线≤5inch。                     |

### 说明

1. WS63V100 系列芯片 UART 接口 RX 管脚不需要接上拉电阻。为防止电源倒灌，建议 WS63 芯片侧串口 RX 不接上拉电阻。

2. WS63V100 系列芯片 UART0/1 接口 TX 管脚为开漏输出，需要接上拉电阻提供高电平驱动能力。为防止通过 WS63 芯片侧 TX 上拉电阻倒灌电源，建议 TX 总线上对端设备不接上拉电阻（对端为 RX 输入管脚，无需上拉）。

3. WS63V100 系列芯片 UART2 接口 TX 管脚有高电平驱动能力，不需要接上拉电阻。为防止电源倒灌，建议 UART2 接口 TX 总线不接上拉电阻。

4. 针对 WS63 单独下电场景，在将 WS63 下电后，建议对端设备 UART 接口主动将 TX、RX 总线驱动低电平。

### 3.3.2 PWM 接口

WS63V100 系列芯片支持 8 个 PWM 接口信号输出，输出电平与 DVDD3318 管脚电平保持一致，占空比输出范围（1/65535 到 1）。设计建议如表 3-15 所示。

表3-15 PWM 接口设计建议

| 名称 | 设计建议 |

|----|------|

|    |      |

| 名称   | 设计建议         |

|------|--------------|

| PWM0 | 直连，走线≤5inch。 |

| PWM1 | 直连，走线≤5inch。 |

| PWM2 | 直连，走线≤5inch。 |

| PWM3 | 直连，走线≤5inch。 |

| PWM4 | 直连，走线≤5inch。 |

| PWM5 | 直连，走线≤5inch。 |

| PWM6 | 直连，走线≤5inch。 |

| PWM7 | 直连，走线≤5inch。 |

### 3.3.3 I2S 接口

WS63V100 系列芯片支持一个 I2S 接口，输入输出电平与 DVDD3318 管脚电平保持一致。设计建议如表 3-16 所示。

表3-16 I2S 接口设计建议

| 名称        | 设计建议     |

|-----------|----------|

| I2S_MCK   | 直连，包地处理。 |

| I2S_DO    | 直连。      |

| I2S_SCLK  | 直连，包地处理。 |

| I2S_LRCLK | 直连，包地处理。 |

| I2S_DI    | 直连。      |

### 3.3.4 QSPI&SPI 接口

WS63V100 系列芯片支持 QSPI 和 SPI 接口，输入输出电平与 DVDD3318 管脚电平保持一致。设计建议如表 3-17 所示。

表3-17 QSPI&amp;SPI 接口设计建议

| 名称       | 设计建议                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_CSN  | 直连，走线≤5inch。                                                                                                                                    |

| SPI_CLK  | 两层板，走线≤5inch，芯片端预留一个串接电阻位置，单根走线包地处理。<br>四层板，DVDD3318=1.8V，走线≤5inch，芯片端预留一个串接电阻位置，单根走线包地处理。<br>四层板，DVDD3318=3.3V，走线≤5inch，芯片端预留一个串接电阻位置，单根走线包地处理 |

| SPI_DATA | 两层板，走线≤5inch，芯片端预留一个串接电阻位置，单根走线包地处理。<br>四层板，走线≤5inch，芯片端预留一个串接电阻位置，单根走线包地处理。                                                                    |

### 3.3.5 I2C 接口

WS63V100 系列芯片支持两组 I2C 接口，与 UART0/UART1 管脚复用。设计建议如表 3-18 所示。

表3-18 I2C 接口设计建议

| 名称                | 设计建议                             |

|-------------------|----------------------------------|

| I2C0_SCL/I2C1_SCL | 直连，走线≤5inch，总线需要上拉，建议上拉电阻 2.2kΩ。 |

| I2C0_SDA/I2C1_SDA | 直连，走线≤5inch，总线需要上拉，建议上拉电阻 2.2kΩ。 |

### 3.3.6 ADC 接口

WS63V100 系列芯片支持 6 个 ADC 接口，ADC 电压量测范围 0.3V ~ 3.3V。设计建议如表 3-19 所示。

表3-19 ADC 接口设计建议

| 名称   | 设计建议                       |

|------|----------------------------|

| AIN0 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

| AIN1 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

| AIN2 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

| AIN3 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

| AIN4 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

| AIN5 | 直连。模拟信号通道，建议两侧包地，远离高速信号干扰。 |

## 3.4 控制信号应用参考设计

WS63V100 系列芯片控制信号及应用如表 3-20 所示。

表3-20 控制信号应用参考设计

| 名称      | 设计建议                                          |

|---------|-----------------------------------------------|

| PWR_ON  | 远离高速信号，建议包地处理，预留上拉 20kΩ到 DVDD3318，220nF 电容接地。 |

| PWR_SEL | 远离高速信号，建议包地处理。                                |

| BUCK_LX | 功率电感靠近芯片放置，减少 BUCK 环路寄生。                      |

## 3.5 RFIO 设计

WS63 系列芯片集成 2.4G WiFi PA 和 LNA，集成 T/R Switch，支持外接单天线，不支持外置 FEM 和外置 LNA。WS63 系列芯片支持 2.4G，支持全球所有国家定义的 WLAN 频段，支持 b/g/n/11ax 协议版本。

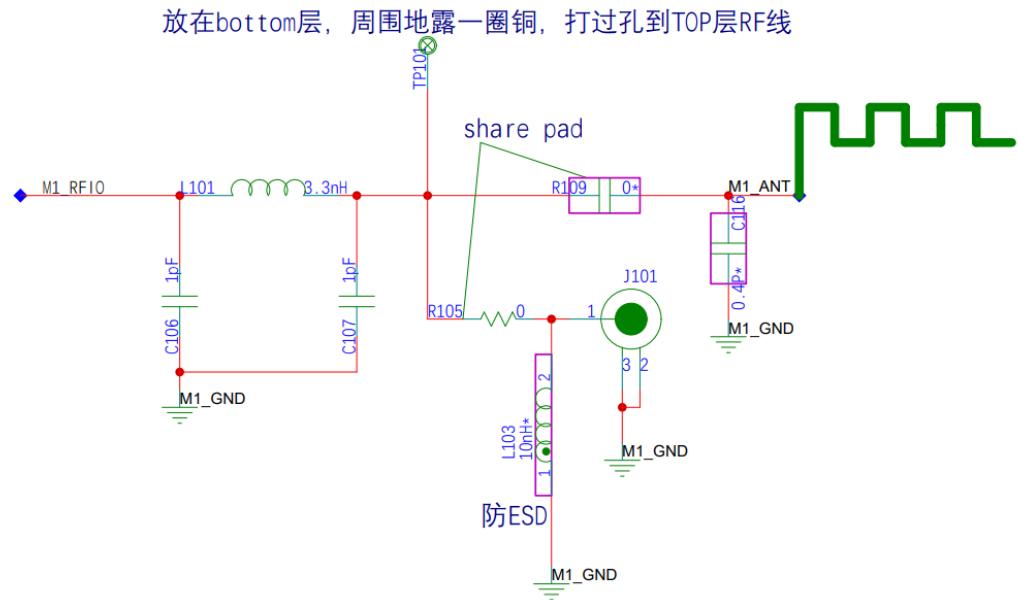

WS63 系列芯片的 PIN1 为 RFIO 管脚，作为 WiFi/BLE/SLE 的接收发送管脚，WS63E 芯片中也可作为雷达发射管脚。射频链路建议使用π型 LC 滤波电路，参考电

路如图 3-16，图中的 LC 滤波为推荐值，LC 滤波及天线匹配电路请根据实际情况调整。RF 连接器旁边建议预留 ESD 器件。

图3-16 RFIO 设计参考电路图

## 3.6 RFI 设计

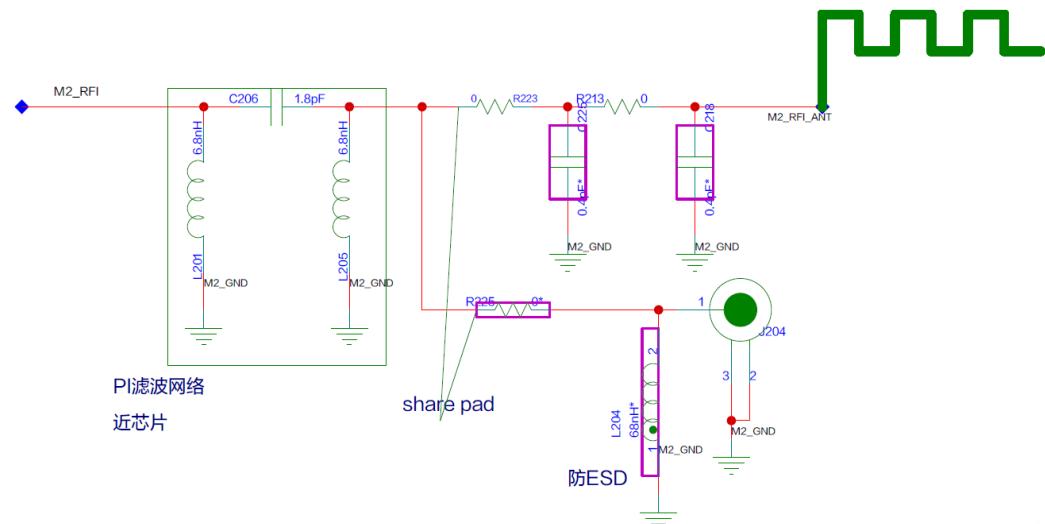

WS63E 芯片提供了雷达检测解决方案，芯片的 PIN40 为 RFI 管脚，作为雷达检测的射频接收管脚。设计中，为防止 EMI 干扰，在 RFI 通路靠近芯片口预留π型 LC 高通滤波器位置，滤除低频干扰。射频通路天线口建议预留π型 LC 匹配电路，参考电路如图 3-17，LC 滤波及天线匹配值请根据实际情况调整。

图3-17 RFI 设计参考电路图

### 说明

雷达板载天线设计仅供参考，用户板载天线需要按照产品需求自行设计测试。

- 板载 PCB 天线需要以整机为基础进行设计、仿真，综合考虑天线净空、模组底板、外壳等环境影响。

- 雷达检测方案天线设计规格约束：RFIO 为雷达 Tx 天线，RFI 为雷达 Rx 天线。Tx、Rx 天线频率 2.4-2.5GHz；VSWR<2；Tx、Rx 射频链路，天线隔离度>=20dBc，射频板级走线隔离度>=32dBc；天线增益>=0dBi；Tx、Rx 天线带内群时延<1ns。

- 雷达检测方案 Tx、Rx 天线保证同极化，天线设计建议均采用板载 PCB 天线。

- RFI 雷达 Rx 天线远离 EMI 干扰源，在 RFI 通路靠近芯片口预留π型 LC 高通滤波器位置，滤除低频干扰。

- 整机设计中，为防止感知误触发，雷达模组应远离机械振动部件（例如蜂鸣器）。

- 为规避人感探测区间，要求整机底板大电流器件如需刷新，刷新率应>100Hz（例如 LED 灯、蜂鸣器）

# 4 PCB 设计建议

- 4.1 叠层和布局

- 4.2 Fanout 封装设计建议

- 4.3 PCB 布局

- 4.4 电源

- 4.5 RF 布线指导

- 4.6 时钟布线指导

- 4.7 GND 布线指导

- 4.8 屏蔽罩

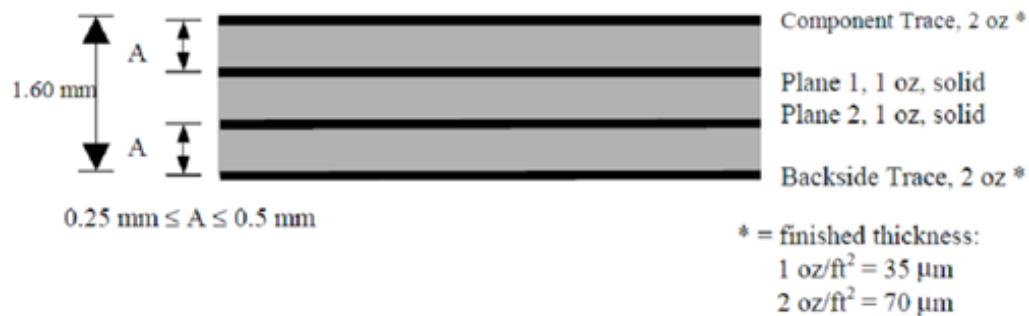

## 4.1 叠层和布局

WS63 系列芯片封装为 QFN40，规格大小为 5mm×5 mm，PCB 支持 2/4 层板，支持器件单面贴设计。

- 两层板分层设计建议：

- TOP 层：信号走线，信号线和电源线尽量走 TOP 层。

- BOTTOM 层：地平面层，尽量保持地平面的完整。

- 四层板分层设计建议：

- TOP 层：信号走线，信号线尽量走 TOP 层。

- 内一层：地平面层，保持一个完整的地平面层。

- 内二层：电源平面层，电源走线尽量走第三层，且电源之间需要用地隔开。

- BOTTOM 层：可以走少量的信号线，尽量保持 BOTTOM 层为一个完整的地平面层。

- PCB 设计注意事项：

- 推荐 PCB 板厚 On Board 方案一般 $\geq$ 1mm，防止翘曲，过孔 8/18 mil。

- PCB 典型材料 FR4 介电常数为 4.0~4.3，表层铜箔厚度建议为 1.2mil (0.5oz+plating)，PCB 板厚度一般 $\geq$ 1.0mm，典型值为 1.2mm，可选用 1.0mm。

- 2 层板设计中，EPAD 和外部地用细线连通，改善 RF 回流。

常用的叠层设计和阻抗控制可参考表 4-1。

表4-1 2 层板 1.0mm 参考叠层信息

| 层标识   | 设计要求层<br>叠图示             | 设计要求介质厚度<br>(oz/mil) | PCB 厂家设计调整<br>介质厚度(oz/mil) | PCB 厂家设计<br>调整层叠图示       |  |

|-------|--------------------------|----------------------|----------------------------|--------------------------|--|

| Art 1 | 0.5oz+plating            |                      |                            | 0.5oz+plating            |  |

|       | CORE                     | 35.4                 | 34.06                      | CORE                     |  |

| Art 2 | 0.5oz+plating            |                      |                            | 0.5oz+plating            |  |

| 板厚    | 客户设计板厚：1.0 $\pm$ 0.10 mm |                      |                            | 厂家理论板厚：1.0 $\pm$ 0.10 mm |  |

表4-2 单线线宽、阻抗、参考层控制信息参考

| 层标识   | 设计线宽                          | 设计阻<br>抗        | 调整线宽                      | 调整阻抗         | 参考层   |

|-------|-------------------------------|-----------------|---------------------------|--------------|-------|

| Art 1 | 5/19/5 (到地距<br>离/线宽/到地距<br>离) | 50 $\pm$<br>10% | 5/19/5 (到地距离/<br>线宽/到地距离) | 50 $\pm$ 10% | L1&L2 |

注：线宽的计量单位为 mil，阻抗的计量单位为 $\Omega$ 。

表4-3 4 层板 1.2mm 参考叠层信息

| 层标识 | 设计要求层<br>叠图示 | 设计要求介质厚<br>度(oz/mil) | PCB 厂家设计调<br>整介质厚度<br>(oz/mil) | PCB 厂家设计<br>调整层叠图示 |

|-----|--------------|----------------------|--------------------------------|--------------------|

|-----|--------------|----------------------|--------------------------------|--------------------|

| 层标识   | 设计要求层叠图示                  | 设计要求介质厚度(oz/mil) | PCB 厂家设计调整介质厚度(oz/mil)    | PCB 厂家设计调整层叠图示 |

|-------|---------------------------|------------------|---------------------------|----------------|

| Art 1 | 0.5oz+plating             |                  | 0.5oz+plating             |                |

|       | PP                        | 8.2              | 10.88                     | PP             |

| Art 2 | 1oz                       |                  | 1oz                       |                |

|       | CORE                      | 23.8             | 18                        | CORE           |

| Art 3 | 1oz                       |                  | 1oz                       |                |

|       | PP                        | 8.2              | 10.88                     | PP             |

| Art 4 | 0.5oz+plating             |                  | 0.5oz+plating             |                |

| 板厚    | 客户设计板厚: $1.2 \pm 0.12$ mm |                  | 厂家理论板厚: $1.2 \pm 0.12$ mm |                |

表4-4 单线线宽、阻抗、参考层控制信息

| 信号层 | 接地层   | 阻抗目标  | 阻抗公差 | 设计线宽(mil) | 距铜(mil) |

|-----|-------|-------|------|-----------|---------|

| L1  | L1&L2 | L1&L2 | 10%  | 11        | 6       |

## 4.2 Fanout 封装设计建议

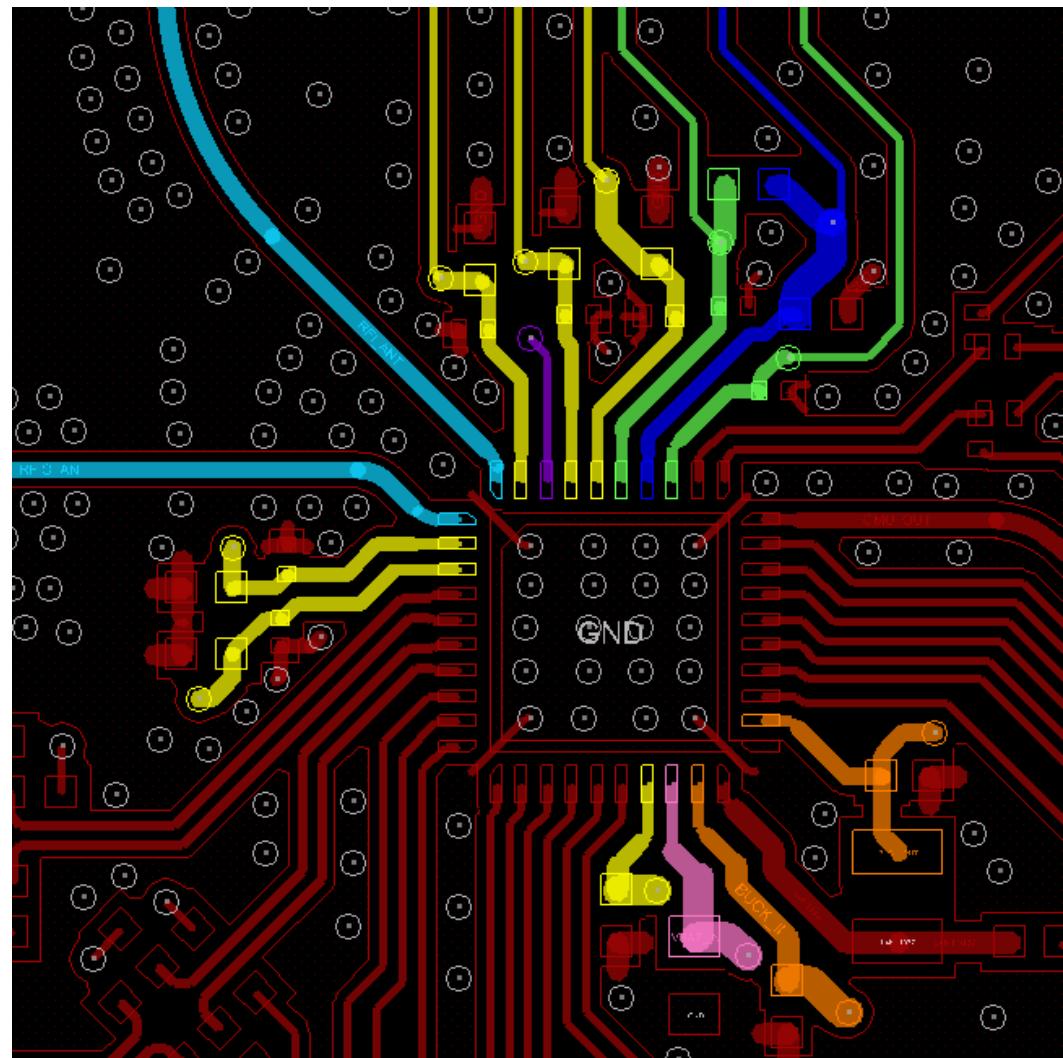

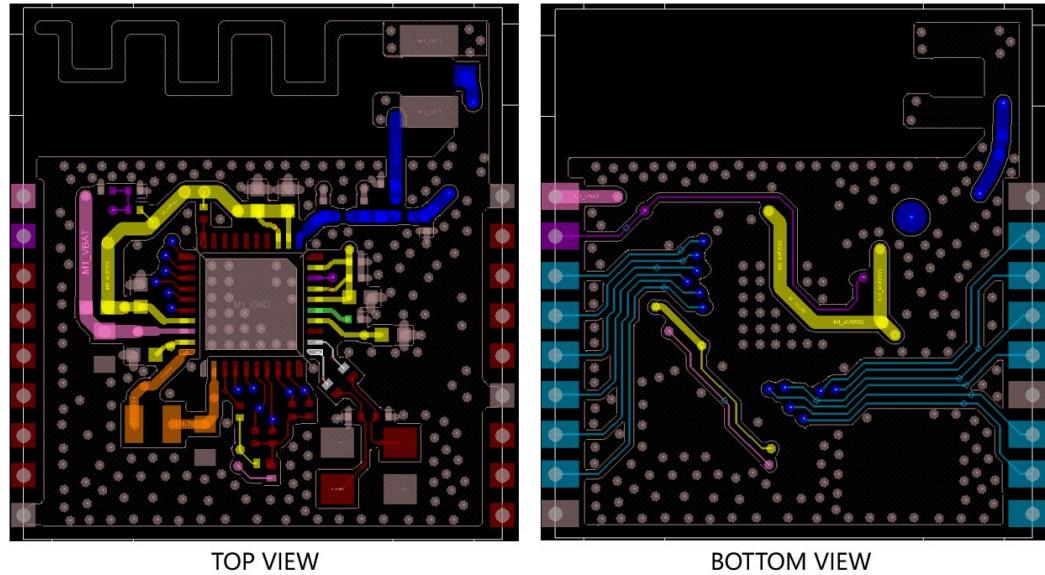

四层板 Fanout 如图 4-1 所示。

图4-1 PCB 四层板 Fanout 参考设计

其中：

- 黄色：AVDD33\_RF0, AVDD33\_RF1, AVDD33\_RF2, AVDD33\_0, AVDD33\_1, VDD33\_OUT

- 绿色：IOLDO18, VDD\_DIG

- 紫色：PWR\_ON

- 深蓝色：DVDD3318

- 淡蓝色：RF\_ANT, RFIO\_ANT

- 橙色：BUCK\_IN, BUCK\_OUT

- 粉色：VBAT\_IN

## 4.3 PCB 布局

应用支持 On Board 和模组两种方案。

- On Board 方案

- 支持 2 层板设计。

- On Board 可双面贴片，空间允许可以选择 0402 封装，空间不足可选择 0201 封装 (inch)。

- 模组

- 建议用 2 层板。

- 贴片器件建议用 0201 封装 (inch)。

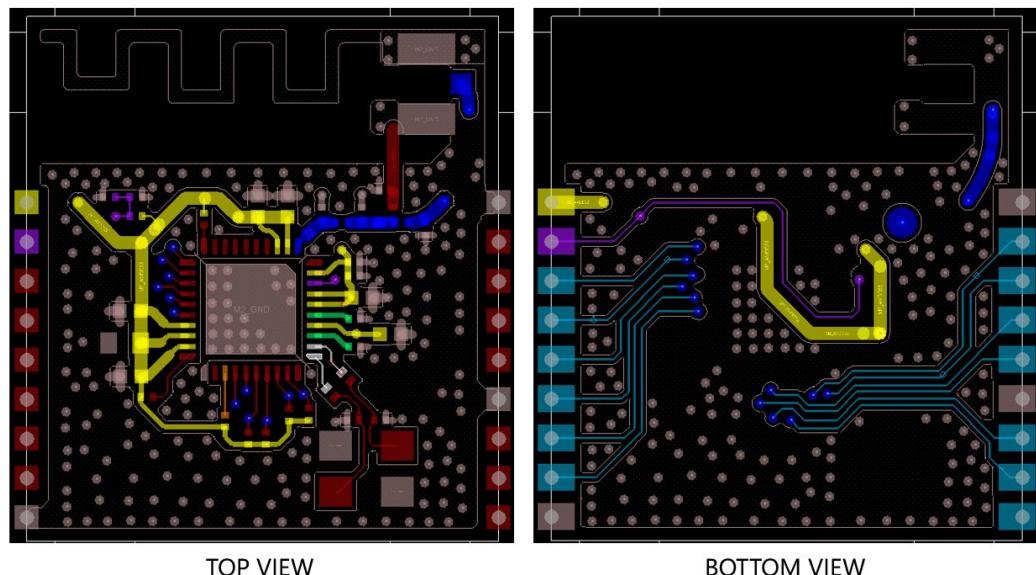

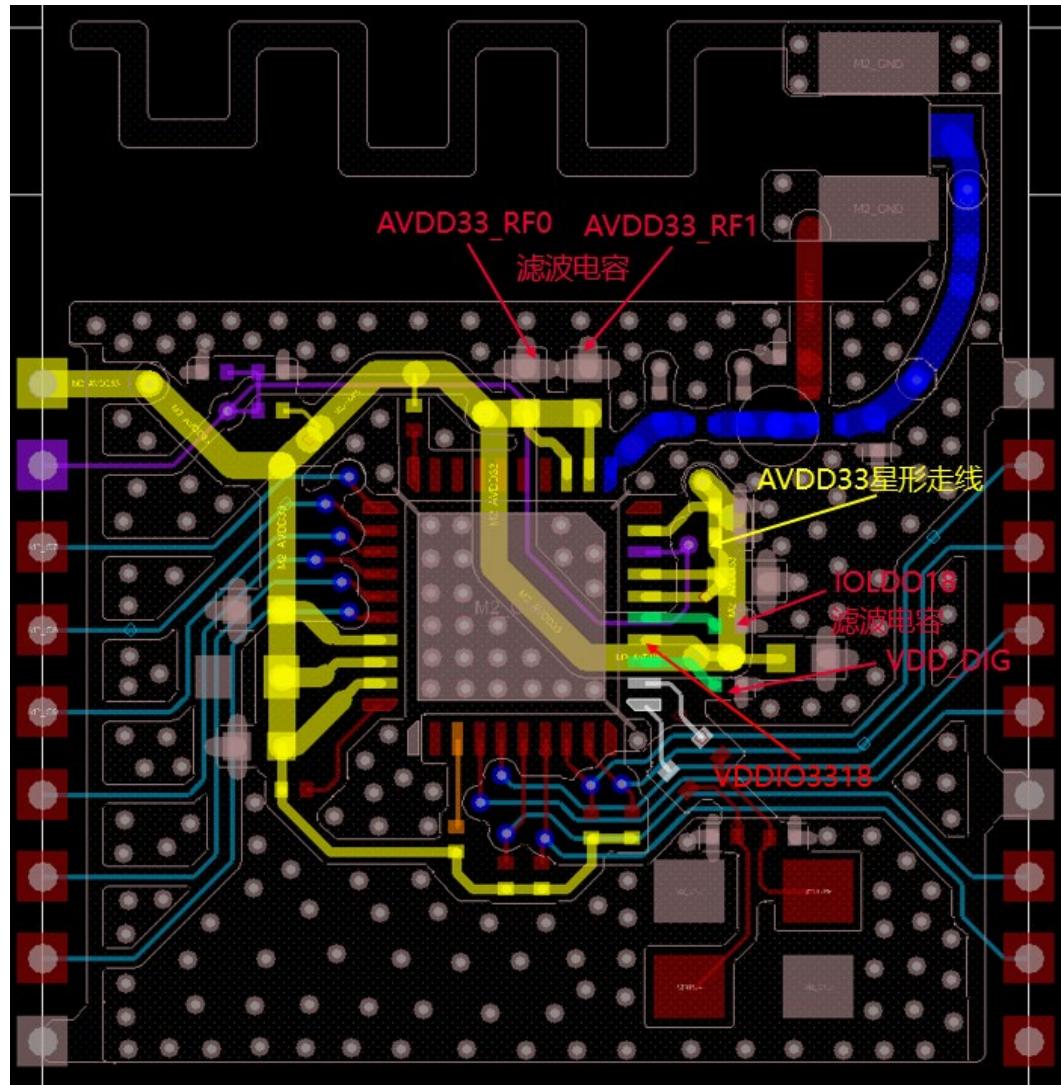

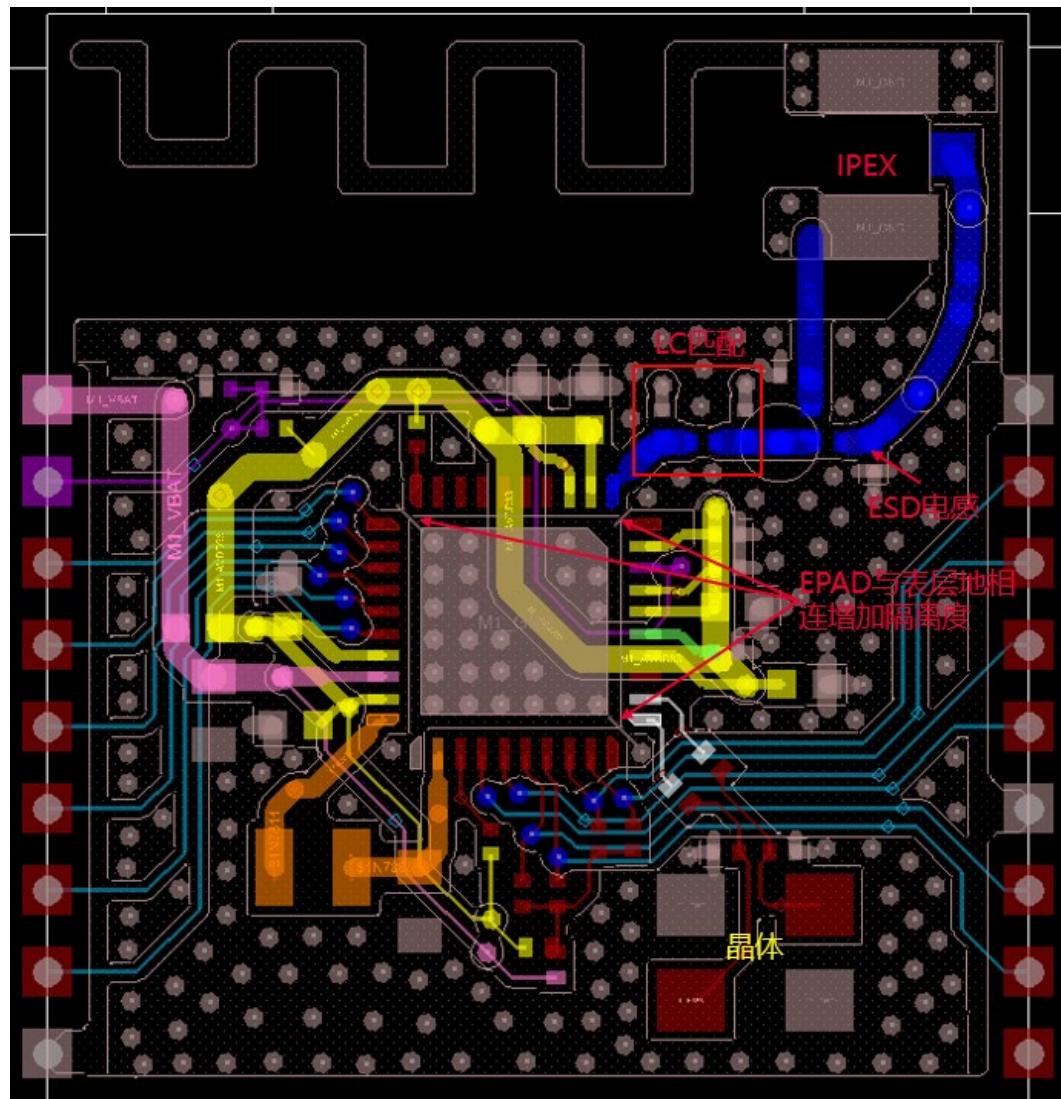

PCB 设计以模组两层板为例，参考设计如图 4-2 和图 4-3 所示。

图4-2 LDO 供电方案模组 PCB 布局参考

其中：

- 黄色：AVDD33\_RF0, AVDD33\_RF1, AVDD33\_RF2, AVDD33\_0, AVDD33\_1, VDD33\_OUT, DVDD3318, BUCK\_IN, VBAT\_IN

- 绿色：IOLDO18, VDD\_DIG

- 紫色：PWR\_ON

- 深蓝色：RFIO\_ANT

- 橙色: BUCK\_OUT

- 白色: XIN, XOUT

图4-3 BUCK 供电方案模组 PCB 布局参考

其中:

- 黄色: AVDD33\_RF0, AVDD33\_RF1, AVDD33\_RF2, AVDD33\_0, AVDD33\_1, VDD33\_OUT, DVDD3318

- 绿色: IOLDO18, VDD\_DIG

- 紫色: PWR\_ON

- 深蓝色: RFIO\_ANT

- 橙色: BUCK\_IN, BUCK\_OUT

- 粉色: VBAT\_IN;

#### 说明

通常 RF 器件布局比较紧凑, 这样会导致近芯片侧π型 LC 滤波网络的两个接地电容的接地过孔靠的比较近, 这样会影响到 RF 的谐波抑制性能, 建议两个接地电容分布在 RF 走线的两边, 这样可以提高 RF 电路的谐波抑制效果。

## 4.4 电源

- 电源走线宽度需要满足“3.2.2 电源规格”中的建议电流值，建议按照 100mA/4mil 的通流能力来设计。

- 所有电源走线需先经过滤波电容再到对应的芯片管脚，滤波电容靠近被滤波芯片管脚放置。电容就近接地，避免长走线引入电感效应。

- RF 电源对外干扰较大，需远离模拟电源和敏感信号。RF 电源各个管脚需要有各自的滤波电容，经过各自的滤波电容后分别走线，避免振荡问题。

- AVDD33 电源走线支持串行走线，但星型走线可以带来更好的性能，图 4-4 黄色走线即为星形走线，深蓝色为 RFIO\_ANT 走线。

AVDD33 电源走线（黄色）、DVDD3318、IOLDO18 及 VDD\_DIG 上的滤波电容摆放位置如图 4-4 所示。

图4-4 模组两层板电源布线参考

## 4.5 RF 布线指导

- RF 走线控制阻抗  $50\Omega$ ，线尽量短不允许有锐角和直角。2 层板采用共面波导设计，走线两边包地多打地孔。

- 硬件设计中，如果射频通道上有引入 ESD 风险的点位，例如裸露的射频测试点、金属天线、外接天线座等，在 ESD 风险点靠近芯片侧 预留 ESD 电感或 TVS 管，增加 ESD 防护能力。

- EPAD 四个角向外走，建议和表层 GND 连接，以增加隔离度。

- RF 匹配滤波电路的π型匹配电路的电容需要单点接地，不能直接在 TOP 层接地。如果是两层板需要打一个过孔连接到 BOTTOM 层的地，如果是多层板过孔不与中间层的地相连，过孔在中间层需要跟 TOP 层一样做禁空处理。这样处理的过孔相当于一个小电感与电容一起组成一个 LC 电路，起到抑制谐波辐射的目的。过孔的位置分布在 RF 线的两边。

图4-5 RF 布线参考

- RF 远离晶体，参考值>5mm，晶体 XOUT 与 RF 的隔离度优于-55dB。

- RF 走线的 S11 参数需要优于-15dB。

- RF1 和 RFIO 隔离度要求-32dB 以上。

- RF 远离时钟线、电源线、DDR 和 CPU 等强干扰源。

- 射频走线参考地保证完整，不允许有交叉、换层。若需要换层，换层孔周围打一圈地孔，形成类同轴结构。

- RF connector、滤波电容电感等大焊盘器件，射频信号对应的 PIN 邻层地需挖空（2 层板除外），避免寄生电容效应射频信号耦合到地。

- IPEX 座子 TOP 层和 BOTTOM 需要就近接地并打地孔。

#### 说明

雷达检测模组 PCB 设计约束：

- 雷达模组与整机底板单点接地，避免与整机底板主地大面积连接。

- 雷达模组电源选择低噪声、低纹波的线性电源，或者与整机底板主供电进行滤波隔离。

- 雷达模组贴片的下方整机底板区域禁止走线、铺铜。

- 雷达模组射频走线避免走在靠近整机底板贴片的电气层，例如常规设计中，模组射频走线不要走 BOTTOM 层，消除底板噪声耦合到模组射频通道的风险。

- 雷达模组接口插针远离天线放置，插针选择 L 型侧接类型，焊接建议选用表贴方式，垂直板面的金属高度尽量短。

## 4.6 时钟布线指导

- 远离天线禁布区，参考值>10mm；远离数据线，参考值>5mm。

- 晶体及其走线远离噪声源和热源。WiFi 系统对时钟要求很高，噪声源（例如 RF、BUCK）会引起系统相噪变差，热源辐射会造成晶体温漂。

- XIN/XOUT 信号走线尽量短，做过孔和包地处理。

- PCB 空间受限的场景，时钟可能会耦合 RF 干扰到芯片内部，建议在 XIN、XOUT 走线靠近芯片端串接一个  $0\Omega$  电阻用于调试。

- PCB 为 4 层板时，晶体的 GND pad 建议在 TOP 层和其他地分割，通过过孔连接到主地，防止单板上的器件发热影响时钟精度。

## 4.7 GND 布线指导

EPAD 四个角向外走 GND 线，和表层 GND 连接。

EPAD 过孔建议打  $6\times 6$  个。两层板受空间限制，EPAD 对应的 BOTTOM 层分 2 个区域。

整机尽量保留一个完整地平面，保证各芯片信号良好共地和回流，完善地孔，避免孤立铜皮出现。

## 4.8 屏蔽罩

TBD

# 5 热设计建议

## 5.1 工作条件

### 5.2 电路热设计参考

## 5.1 工作条件

### 须知

- 芯片的极限结温的最大值为 125°C，任何条件下芯片的结温都不能大于该数值。

- 芯片的长期工作结温的最大值为 105°C，正常工作条件下芯片的结温应该小于该数值。

- 在短期工作条件下，芯片可以容忍超过 105°C（长期工作结温的最大值）而小于 125°C（极限结温的最大值）的高温，但长时间工作在超过 105°C（长期工作结温的最大值）结温下会导致芯片寿命缩减。

表5-1 芯片的结温要求

| 封装形式 | 正常工作结温下限(°C) | 长期工作最大结温(°C) | 短期工作上限结温(°C) | 破坏性最大结温(°C) | 生命周期定义 |

|------|--------------|--------------|--------------|-------------|--------|

| QFN  | -40          | 105          | 125          | 125         | 10 年   |

表5-2 芯片的封装热阻

| 参数                                                | 符号            | WS63 系列<br>芯片 | 单位   |

|---------------------------------------------------|---------------|---------------|------|

| Junction-to-ambient thermal resistance            | $\theta_{JA}$ | 57.0          | °C/W |

| Junction-to-case thermal resistance               | $\theta_{JC}$ | 27.7          | °C/W |

| Junction-to-top center of case thermal resistance | $\Psi_{JT}$   | -             | °C/W |

| Junction-to-board thermal resistance              | $\theta_{JB}$ | 19.44         | °C/W |

备注：热阻基于 JEDEC JESD51-2 标准给出，应用时的系统设计及环境可能与 JEDEC JESD51-2 标准不同，需要根据应用条件作出分析。

上述封装热阻参数仿真环境是 JEDEC 标准的 4 层 PCB，如图 5-1 所示。

图5-1 JEDEC 标准的 4 层 PCB 参数

## 5.2 电路热设计参考

芯片硬件方案设计时，推荐采用 3V3\_BUCK 供电方案，实现更好的性能表现。

5V\_BUCK 方案和 3V3\_LDO 方案仅建议在低功耗场景下采用，且应用场景中芯片位置板温建议不超过 70°C。

### 5.2.1 器件布局

结合产品结构和热设计，器件布局建议如下：

- 单板上大功耗且易产生热量器件要均匀分布，避免局部过热，影响器件可靠性和散热效率。

- 合理设计结构，保证产品内部与外界有热交换途径。

- 对单板关键发热器件充分进行极端应用场景的温升测试，确保器件在安全的温度范围内长期可靠工作。

- 必要情况下，关键发热器件可以增加散热片，进一步提升散热效果。

## 5.2.2 PCB

走线热设计建议如下：

- 芯片底下的过孔采用 FULL 孔连接，而不是普通的花孔连接，以提高单板散热效率。

- 在热量大的器件正下方和周边尽量增大铜皮面积，特别是双面 PCB 单板，发热器件背面的地平面尽量减少分割，完整地平面能够有效分散热量，提高整体散热效果。另外，如果结构允许，将芯片正背面附近地平面进行亮铜处理，也能够进一步提升散热效果。

# 6 焊接工艺

## 6.1 概述

6.2 无铅回流焊工艺参数要求

6.3 混合回流焊工艺参数要求

## 6.1 概述

【目的】 Objective

本章规定了客户端在用 SMT 时各温区温度基本设置。

【适用范围】 Scope

芯片产品。

【基本信息】 Basic information

本章主要介绍客户端在使用芯片做回流焊时工艺控制：主要是无铅工艺和混合工艺两类。

【回流焊工艺控制】 Reflow Chart

定义说明：

- 芯片：均满足无铅要求。

- 无铅工艺：所有器件(主板/所有 IC/电容电阻等)均为无铅器件，并使用无铅锡膏的纯无铅工艺。

## 6.2 无铅回流焊工艺参数要求

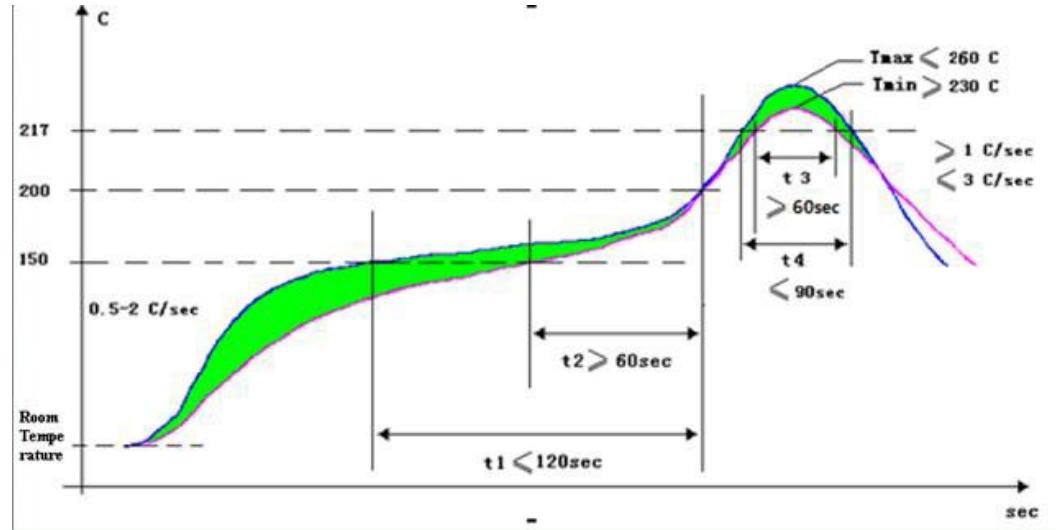

无铅回流焊工艺曲线如图 6-1 所示。

图6-1 无铅回流焊接工艺曲线

无铅回流焊工艺参数如表 6-1 所示。

表6-1 无铅回流焊工艺参数

| 区域                                                | 时间         | 升温速率                         | 峰值温度                           | 降温速率                                                                 |

|---------------------------------------------------|------------|------------------------------|--------------------------------|----------------------------------------------------------------------|

| 预热区 (40 ~ 150°C)                                  | 60 ~ 150 s | $\leq 2.0^{\circ}\text{C/s}$ | -                              | -                                                                    |

| 均温区 (150 ~ 200°C)                                 | 60 ~ 120 s | $< 1.0^{\circ}\text{C/s}$    | -                              | -                                                                    |

| 回流区 ( $> 217^{\circ}\text{C}$ )                   | 60 ~ 90 s  | -                            | $230 \sim 260^{\circ}\text{C}$ | -                                                                    |

| 冷却区 ( $T_{\text{max}} \sim 180^{\circ}\text{C}$ ) | -          | -                            | -                              | $1.0^{\circ}\text{C/s} \leq \text{Slope} \leq 4.0^{\circ}\text{C/s}$ |

说明：

- 预热区：温度由 40°C ~ 150°C，温度上升速率控制在 2°C/s 左右，该温区时间为 60s ~ 150s。

- 均温区：温度由 150°C ~ 200°C，稳定缓慢升温，温度上升速率小于 1°C/s，且该区域时间控制在 60s ~ 120s（注意：该区域一定缓慢受热，否则易导致焊接不良）。

- 回流区：温度由 217°C ~ Tmax ~ 217°C，整个区间时间控制在 60s ~ 90s。

- 冷却区：温度由 Tmax ~ 180°C，温度下降速率最大不能超过 4°C/s。

- 温度从室温 25°C 升温到 250°C 时间不应该超过 6min。

- 该回流焊曲线仅为推荐值，客户端需根据实际生产情况做相应调整。

- 回流时间以 60s ~ 90s 为目标，对于一些热容较大无法满足时间要求的单板可将回流时间放宽至 120s。封装体耐温标准参考 IPC/JEDEC J-STD-020D 标准，封装体测温方法参考 JEP 140 标准。

IPC/JEDEC J-STD-020D 标准，封装体测温方法按照 JEP 140 标准要求：IPC/JEDEC 020D 中的无铅器件封装体耐温标准如表 6-2 所示。

表6-2 IPC/JEDEC 020D 中的无铅器件封装体耐温标准

| Package Thickness | Volume mm <sup>3</sup><br>< 350 | Volume mm <sup>3</sup><br>350 ~ 2000 | Volume mm <sup>3</sup><br>> 2000 |

|-------------------|---------------------------------|--------------------------------------|----------------------------------|

| < 1.6mm           | 260°C                           | 260°C                                | 260°C                            |

| 1.6mm ~ 2.5mm     | 260°C                           | 250°C                                | 245°C                            |

| > 2.5mm           | 250°C                           | 245°C                                | 245°C                            |

体积计算中不计入器件焊端（焊球，引脚）和外部散热片。

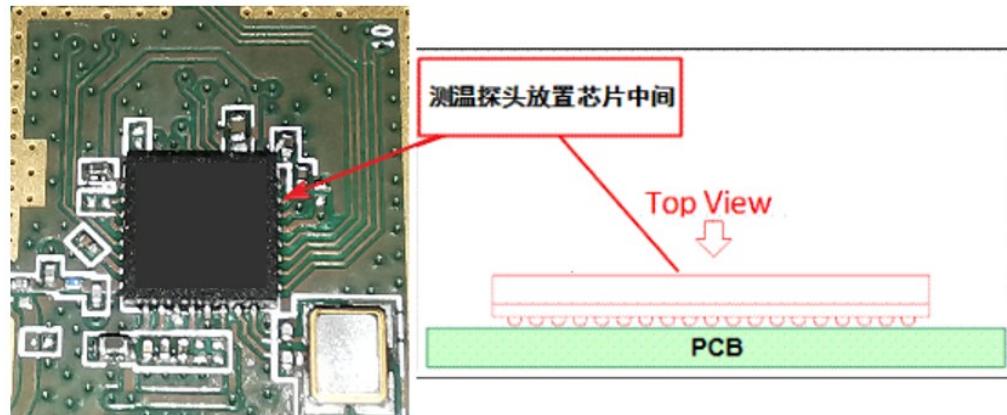

回流焊接工艺曲线测量方法：

JEP140 推荐：对于厚度较小的器件，测量封装体温度时，直接将热电偶贴放在器件表面，对于厚度较大的器件，在器件表面钻孔埋入热电偶进行测量。由于量化器件厚度的要求，推荐全部采用在封装体表面钻孔埋入热电偶的方式（特别薄器件，无法钻孔除外）。如图 6-2 所示。

图6-2 封装体测温示意图

### 说明

如果是 QFP 封装的芯片，直接将测温探头放在管脚处即可。

## 6.3 混合回流焊工艺参数要求

回流焊接过程中，如果出现器件混装现象，应首先保证无铅器件的正常焊接。具体要求如表 6-3 所示。

表6-3 混装回流焊工艺参数表

| 数值要求                   |      | 有铅 BGA                    | 无铅 BGA          | 其它器件            |

|------------------------|------|---------------------------|-----------------|-----------------|

| 预热区<br>(40°C ~ 150°C)  | 时间   | 60s ~ 150s                |                 |                 |

|                        | 升温斜率 | < 2.5°C/s                 |                 |                 |

| 均温区<br>(150°C ~ 183°C) | 时间   | 30s ~ 90s                 |                 |                 |

|                        | 升温斜率 | < 1.0°C/s                 |                 |                 |

| 回流区 (> 183°C)          | 峰值温度 | 210°C~240°C               | 220°C<br>~240°C | 210°C<br>~245°C |

|                        | 时间   | 30s~120s                  | 60s~120s        | 30s~120s        |

| 冷却区 (Tmax ~            | 降温斜率 | 1.0°C/s ≤ Slope ≤ 4.0°C/s |                 |                 |

| 数值要求   | 有铅 BGA | 无铅 BGA | 其它器件 |

|--------|--------|--------|------|

| 150°C) |        |        |      |

### 说明书

以上工艺参数要求均针对焊点温度。单板上焊点最热点和最冷点均需要满足以上规范要求。

曲线调制中，还需要满足单板上元器件的封装体耐温要求。封装体耐温标准按照 IPC/JEDEC J-STD-020D 标准，封装体测温方法按照 JEP 140 标准。

IPC/JEDEC 020D 中的有铅器件封装体耐温标准如表 6-4 所示。

表6-4 IPC/JEDEC 020D 中的有铅器件封装体耐温标准

| Package Thickness | Volume mm <sup>3</sup><br>< 350 | Volume mm <sup>3</sup><br>≥350 |

|-------------------|---------------------------------|--------------------------------|

| < 2.5mm           | 235°C                           | 220°C                          |

| ≥2.5mm            | 220°C                           | 220°C                          |

体积计算中不计入器件焊端（焊球，引脚）和外部散热片。

JEP140 标准规定测量封装体温度方法同无铅工艺，请参考 6.2 无铅回流焊工艺参数要求要求详细说明。

# 7 潮敏参数

## 7.1 存放与使用

### 【使用范围】

所有潮敏产品的存放和使用。

### 【存放环境】

建议产品真空包装存放，存放温度范围： $\geq -40^{\circ}\text{C}$ ,  $\leq 150^{\circ}\text{C}$ 。推荐存放在  $25^{\circ}\text{C}$  的环境温度下。

### 【存储期限】(shelf life)

存放环境 $< 30^{\circ}\text{C}/60\% \text{ RH}$  下，真空包装存放，存储期限(shelf life)不少于 12 个月。

### 【车间寿命】(floor life)

在环境条件 $< 30^{\circ}\text{C}/60\%$ 下，floor life 参照表如表 7-1 所示。

表7-1 车间寿命 (floor life) 参照表

| 潮湿敏感等级<br>(MSL) | 含义 (即拆分后存放条件及最长时间)                                                      |

|-----------------|-------------------------------------------------------------------------|

| 1               | 无限制，环境温湿度 $\leq 30^{\circ}\text{C}/85\% \text{ RH}$ (Relative Humidity) |

| 2               | 1year, $30^{\circ}\text{C}/60\% \text{ RH}$ 。                           |

| 潮湿敏感等级<br>(MSL) | 含义 (即拆分后存放条件及最长时间)         |

|-----------------|----------------------------|

| 2a              | 4week, 30°C/60%RH。         |

| 3               | 1week, 30°C/60%RH。         |

| 4               | 72h, 30°C/60%RH。           |

| 5               | 48h, 30°C/60%RH。           |

| 5a              | 24h, 30°C/60%RH。           |

| 6               | Time on Label, 30°C/60%RH。 |

### 【潮敏产品的使用】

- 产品在≤30°C/60%RH 下连续或累计暴露超过 2 个小时，建议进行重新烘烤后再真空干燥包装。

- 产品在≤30°C/60%RH 下暴露累计没有超过 2 个小时，可以不用重新烘烤，但要更换新的干燥剂，进行真空干燥包装。

- 本产品的潮敏参数等级为 3 级。

本文没有提到的存储及使用原则，请直接参考 JEDEC J-STD-033A。

## 7.2 重新烘烤

### 【适用产品】

所有潮敏产品

### 【使用范围】

需要重新烘烤的潮敏产品

### 【重新烘烤参考表】

表7-2 重新烘烤参考表

| 芯片厚度 | MSL 潮敏等级 | 烘烤 125°C | 烘烤 90°C/≤5% RH | 烘烤 40°C/≤5% RH |

|------|----------|----------|----------------|----------------|

|      |          |          |                |                |

| 芯片厚度         | MSL 潮敏等级 | 烘烤 125°C | 烘烤 90°C/ $\leq$ 5% RH | 烘烤 40°C/ $\leq$ 5% RH |

|--------------|----------|----------|-----------------------|-----------------------|

| $\leq$ 1.4mm | 2a       | 3h       | 11h                   | 5day                  |

|              | 3        | 7h       | 23h                   | 9day                  |

|              | 4        | 7h       | 23h                   | 9day                  |

|              | 5        | 7h       | 24h                   | 10day                 |

|              | 5a       | 10h      | 24h                   | 10day                 |

| $\leq$ 2.0mm | 2a       | 16h      | 2day                  | 22day                 |

|              | 3        | 17h      | 2day                  | 23day                 |

|              | 4        | 20h      | 3day                  | 28day                 |

|              | 5        | 25h      | 4day                  | 35day                 |

|              | 5a       | 40h      | 6day                  | 56day                 |

| $\leq$ 4.5mm | 2a       | 48h      | 7day                  | 67day                 |

|              | 3        | 48h      | 8day                  | 67day                 |

|              | 4        | 48h      | 10day                 | 67day                 |

|              | 5        | 48h      | 10day                 | 67day                 |

|              | 5a       | 48h      | 10day                 | 67day                 |

### 说明

- 此表中显示的均是受潮后，必须的最小的烘烤时间。

- 重新烘烤优先选择低温烘烤。

- 详细情况请参考 JEDEC。

# 8 接口时序

## 8.1 UART 时序

### 8.2 I2C 时序

### 8.3 I2S 时序

### 8.4 SPI 时序

## 8.1 UART 时序

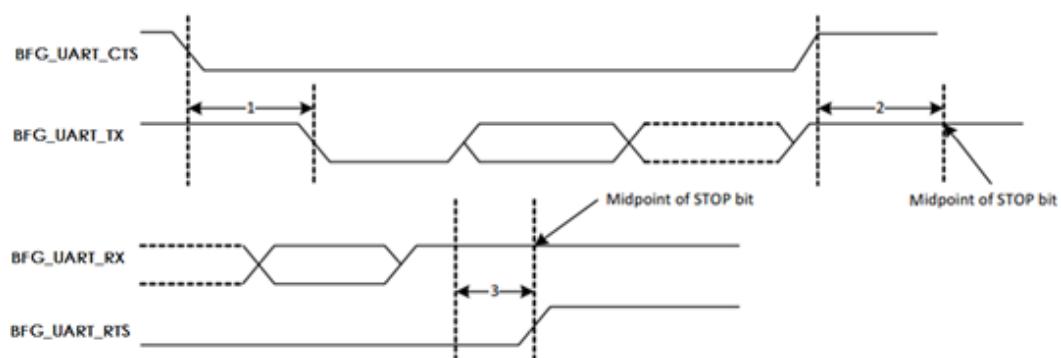

WS63 系列芯片支持 3 组 UART 接口，其中 UART0 口支持两线连接（RXD、TXD），不支持流控模式，最大波特率 2Mbit/s。UART1/UART2 支持四线的协议（RXD、TXD、CTS、RTS），其中 RXD 和 TXD 用于数据传送，RTS 和 CTS 用于流控，最大波特率 5Mbit/s。UART 接口支持多种波特率，波特率大小和传送速率之间成正比关系，其速率可以通过寄存器进行配置。串口发送波特率误差小于 0.5%，串口接收波特率误差容忍度小于 1.5% ，UART 接口的时序如图 8-1 所示。

图8-1 UART 接口时序图

注：图中虚线的信号上升沿按照  $0.7 \times VDD$ ，下降沿按照  $0.3 \times VDD$  选取。

其中：

- 标注 1 为 CTS 信号拉低到 TXD 信号有效的最大延时。

- 标注 2 为结束位的中点到 CTS 信号拉高需要保持的最大时间。

- 标注 3 为结束位的中点到 RTS 信号拉高的最大延时。

UART 时序约束如表 8-1 所示。

表8-1 UART 时序约束表

| Ref No | Characteristics                 | Min. | Typical | Max. | Unit        |

|--------|---------------------------------|------|---------|------|-------------|

| 1      | CTS low to TXD valid            | -    | -       | 1.5  | Bit Periods |

| 2      | CTS high before mid of stop bit | -    | -       | 0.5  | Bit Periods |

| 3      | Mid of stop bit to RTS high     | -    | -       | 0.5  | Bit Periods |

## 8.2 I2C 时序

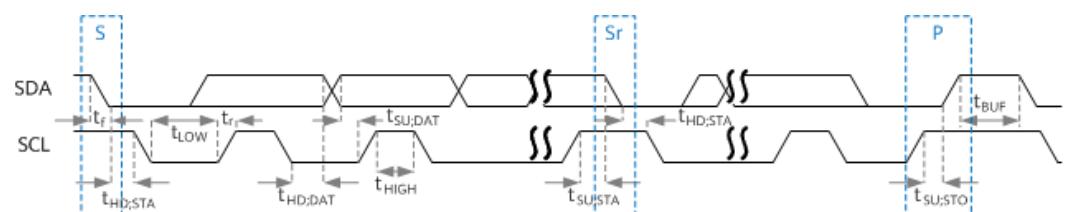

I2C 接口只支持 master 模式，接口传输时序如图 8-2 所示。

图8-2 I2C 传输时序图

I2C 接口时序参数如所示。

表8-2 I2C 接口时序参数表

| 参数 | 符号 | 标准模式最小值 | 标准模式最大值 | 快速模式最小值 | 快速模式最大值 | 单位 |

|----|----|---------|---------|---------|---------|----|

|    |    |         |         |         |         |    |

| 参数           | 符号           | 标准模式最小值 | 标准模式最大值 | 快速模式最小值     | 快速模式最大值 | 单位      |

|--------------|--------------|---------|---------|-------------|---------|---------|

| SCL 时钟频率     | $f_{SCL}$    | -       | 100     | -           | 400     | kHz     |

| 启动保持时间       | $t_{HD;STA}$ | 4.0     | -       | 0.6         | -       | $\mu s$ |

| SCL 低电平周期    | $t_{LOW}$    | 4.7     | -       | 1.3         | -       | $\mu s$ |

| SCL 高电平周期    | $t_{HIGH}$   | 4.0     | -       | 0.6         | -       | $\mu s$ |

| 启动建立时间       | $t_{SU;STA}$ | 4.7     | -       | 0.6         | -       | $\mu s$ |

| 数据保持时间       | $t_{HD;DAT}$ | 0       | 3.45    | 0           | 0.9     | $\mu s$ |

| 数据建立时间       | $t_{SU;DAT}$ | 250     | -       | 100         | -       | ns      |

| SDA、SCL 上升时间 | $t_r$        | -       | 1000    | $20+0.1C_b$ | 300     | ns      |

| SDA、SCL 下降时间 | $t_f$        | -       | 300     | $20+0.1C_b$ | 300     | ns      |

| 结束建立时间       | $t_{SU;STO}$ | 4.0     | -       | 0.6         | -       | $\mu s$ |

| 开始与结束之间的总线释放 | $t_{BUF}$    | 4.7     | -       | 1.3         | -       | $\mu s$ |

| 参数      | 符号       | 标准模式最小值     | 标准模式最大值 | 快速模式最小值     | 快速模式最大值 | 单位 |

|---------|----------|-------------|---------|-------------|---------|----|

| 时间      |          |             |         |             |         |    |

| 总线负载    | $C_b$    | -           | 400     | -           | 400     | pF |

| 低电平噪声容限 | $V_{nL}$ | $0.1V_{DD}$ | -       | $0.1V_{DD}$ | -       | V  |

| 高电平噪声容限 | $V_{nH}$ | $0.2V_{DD}$ | -       | $0.2V_{DD}$ | -       | V  |

## 8.3 I2S 时序

I2S 接口支持 Master/Slave 模式，接口时序 TBD。

## 8.4 SPI 时序

### 说明书

以下缩略语或字母含义：

- MSB: Most Significant Bit

- LSB: Least Significant Bit

- SPI\_CK(0): spo=0

- SPI\_CK(1): spo=1

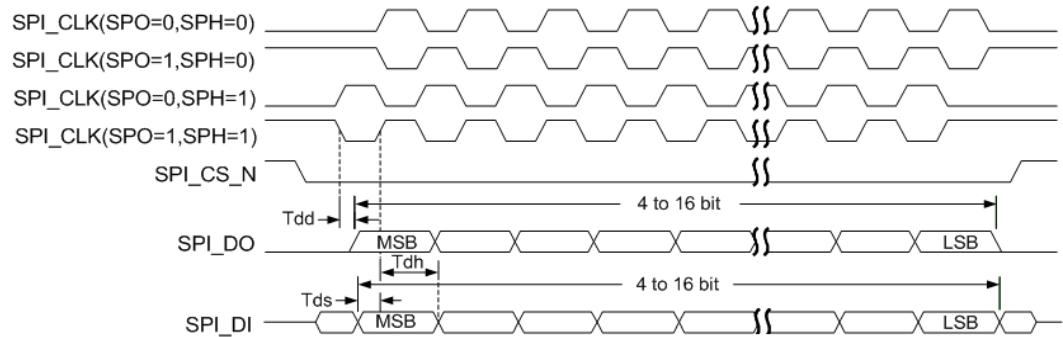

标准 SPI 接口 (SPI0) 支持 Master/Slave 模式，接口时序如图 8-3 所示。

图8-3 SPI 接口时序图

注：用作 Master 时，时钟周期最小值为 80ns；用作 Slave 时，时钟周期最小值为 80ns。

SPO (SPICLKOUT Polarity) 表示 SPICLKOUT 极性，SPH (SPICLKOUT Phase) 表示 SPICLKOUT 相位。

表8-3 SPI 接口时序参数表

| 参数                 | 符号       | 最小值 | 最大值  | 单位 |

|--------------------|----------|-----|------|----|